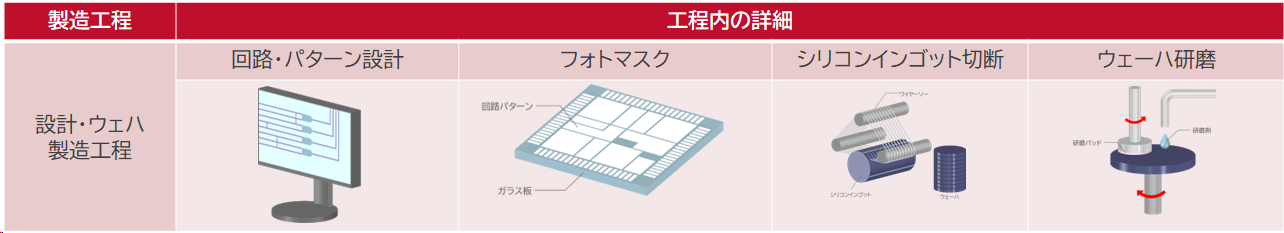

設計・ウェハ製造工程へのCAEの活用

半導体製造プロセスソリューション

設計・ウェハ製造工程とは

半導体回路の設計およびシリコンウェハの製造までの工程です。

設計・ウェハ製造工程の課題とCAE活用事例

課題

ウェハ製造工程では、結晶成長の品質管理や不純物の排除が求められ、さらにウェハの均一性を保ちながら大量生産することや、製造コストの削減とプロセスの最適化も重要な課題になっています。

設計・ウェハ製造工程へのCAE活用事例

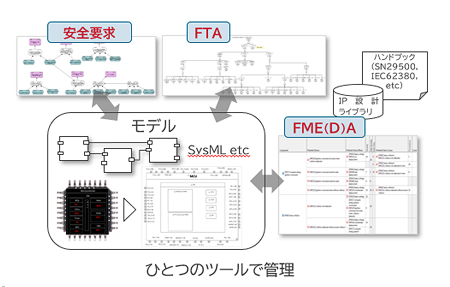

半導体の機能安全設計

安全確保としてヒューマンエラーの未然防止や、規格準拠結果の提示は必須です。要求、分析、仕様等を別々のドキュメントで管理し、レビューやトレーサビリティに時間がかかります。

これらを一つのツールに統合管理し、トレーサビリティや妥当性を自動チェックが可能が可能となる事例をご紹介します。

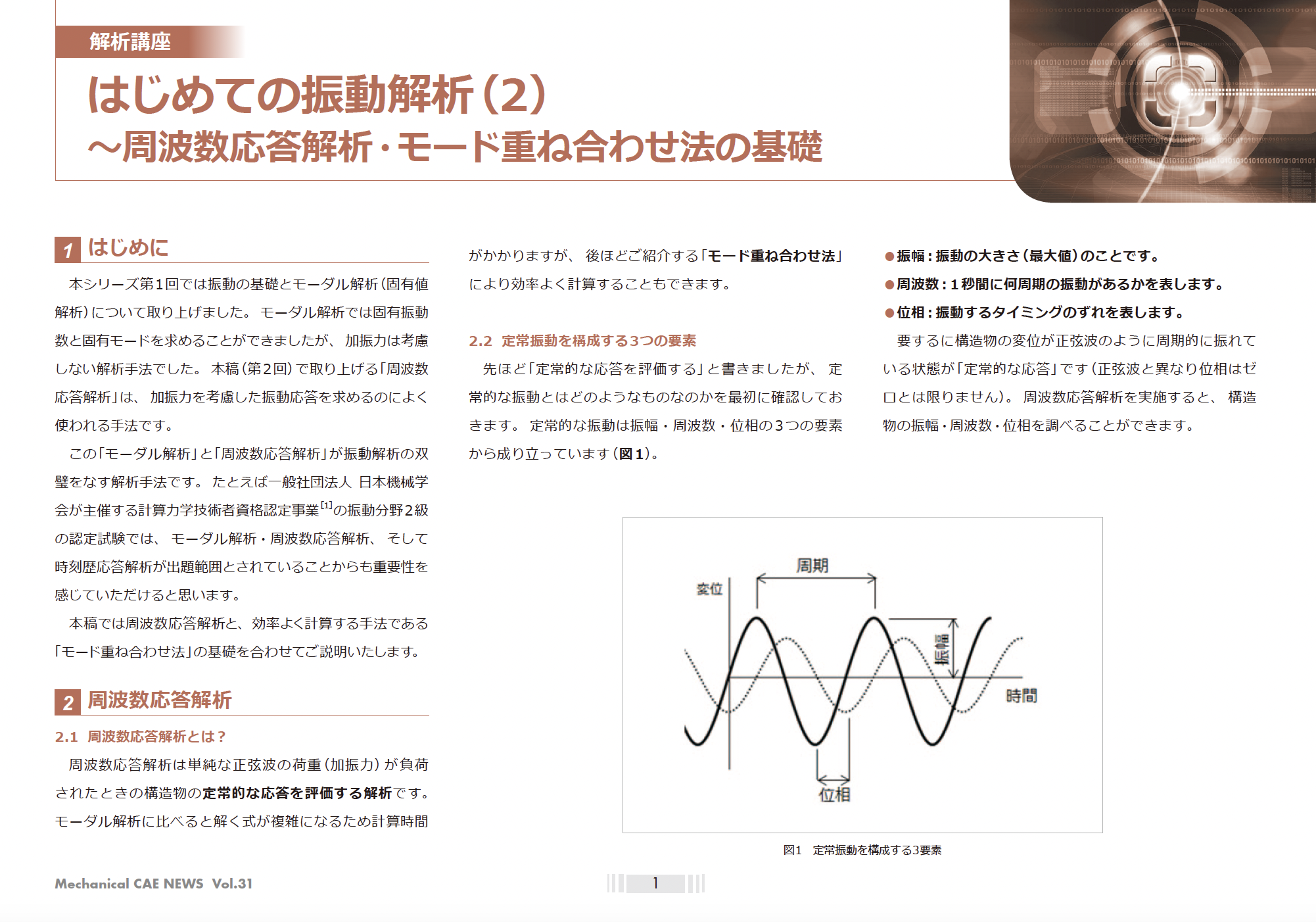

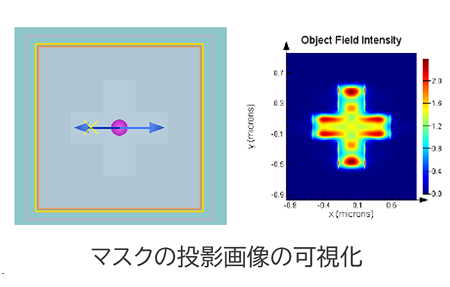

マスク設計における光強度の影響可視化

マスク厚が非常に薄いことでマスク透過後の光の振る舞いがレジスト膜上の光強度分布に影響を与えることが考えられます。

FDTD解析により電磁場光学的的な光の扱いを考慮した解析が可能です。マスク設計に光学解析を活用した事例をご紹介します。

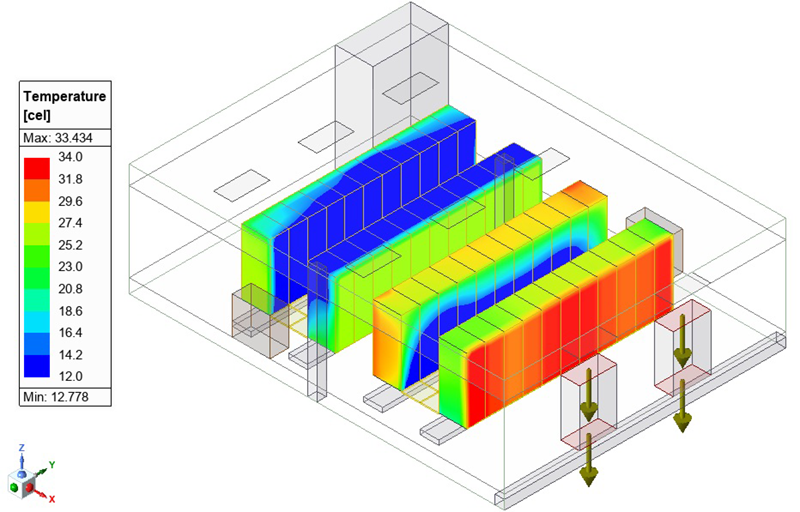

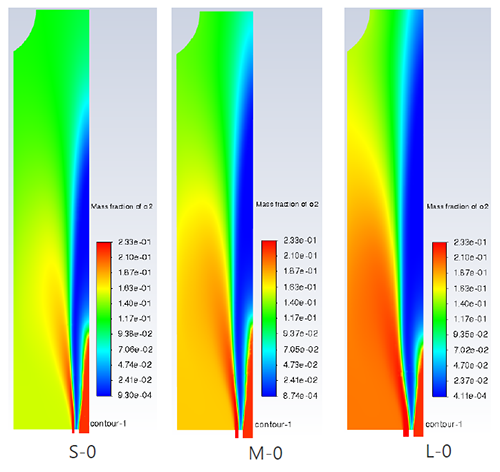

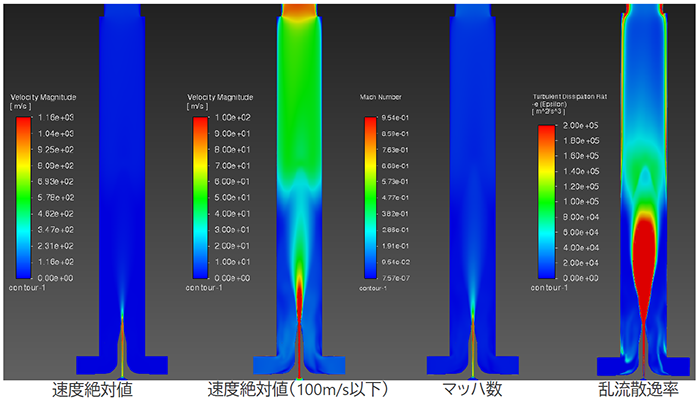

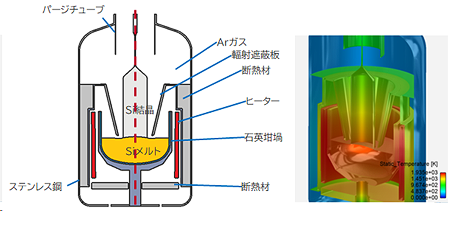

CZ炉における単結晶育成の最適化検討

結晶の品質向上には、運転条件の最適化が重要であるが実験には多くのコスト、時間が掛かります。

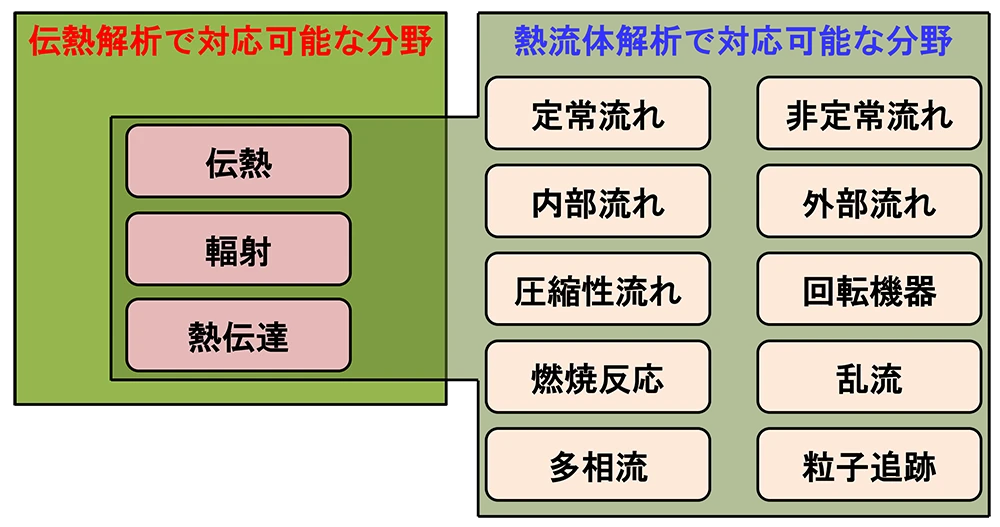

輻射、メルトの流動、アルゴンガスの流れ、坩堝・結晶の回転といった諸条件を考慮した熱流体解析による炉の設計、運転条件検討を行った事例をご紹介します。

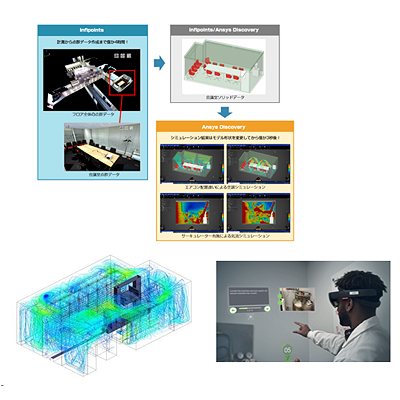

クリーンルーム設計・運用ソリューション

クリーンルーム設計では、目に見えない微粒子の可視化、最適な気流制御を図りたいが、気密性・温度・湿度・圧力・殺菌方法など、検討にはコストが掛かります。

室内の3Dスキャンにより設備を含む3D CAD形状を作成し、流れや照度分布により最適な運用条件を迅速に検討可能となる。運用時にもARの活用によるペーパーレス作業支援が可能となります。

その他の工程はこちら

関連情報

関連する解析事例

MORE関連する資料ダウンロード

MORE-

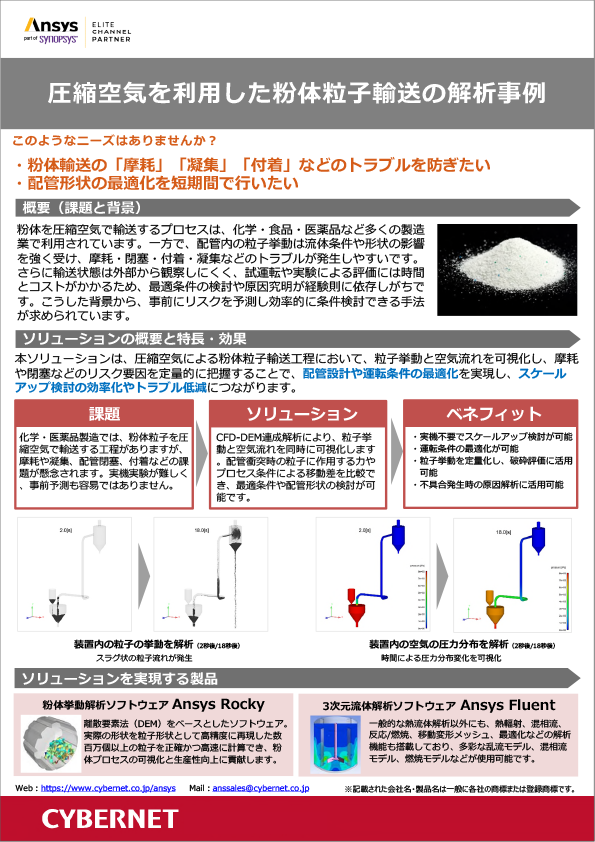

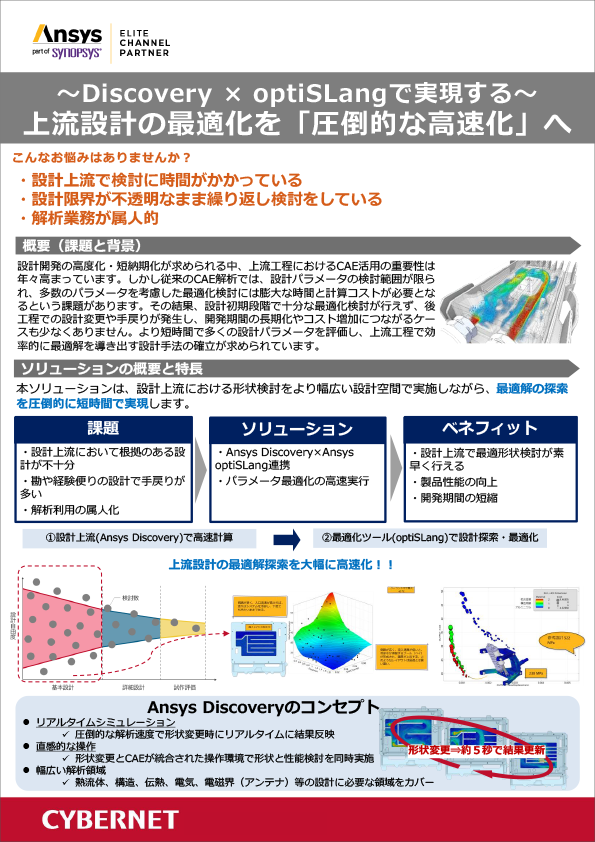

短時間で設計パラメータを評価。上流設計の最適化を「圧倒的な高速化」へ

設計上流における形状検討をより幅広い設計空間で実施

-

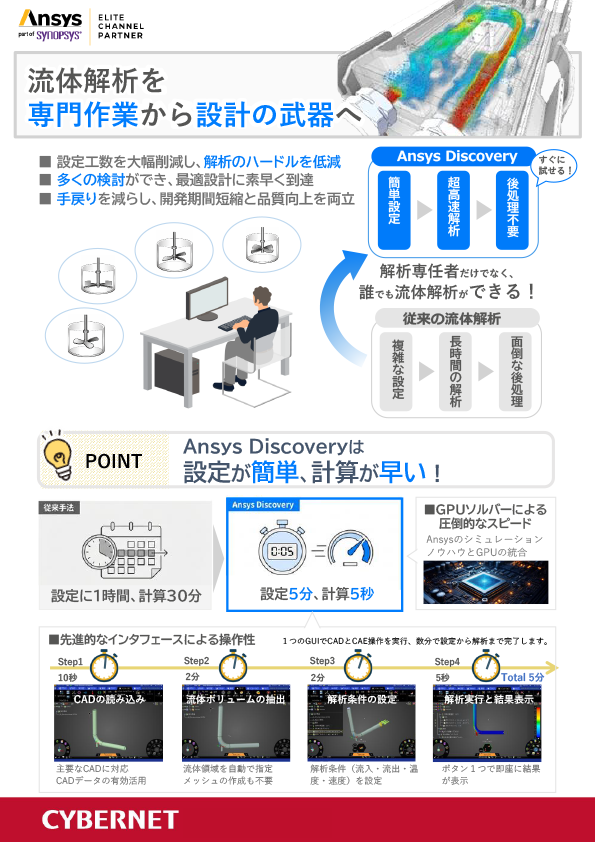

解析専任者だけでなく誰でも解析ができる!設計者のための超高速リアルタイム解析

流体解析を専門作業から設計の武器へ

-

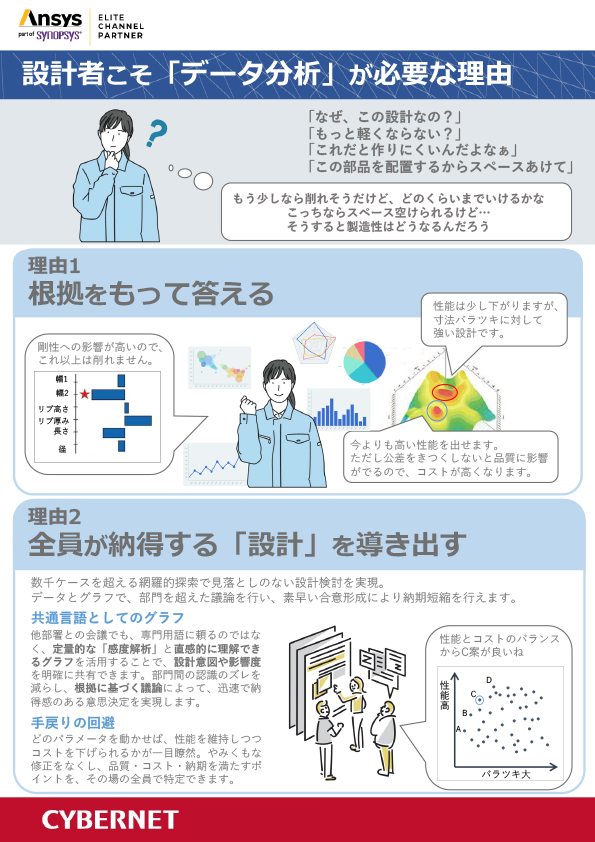

物理状態と統計データの可視化で意思決定の高速化を実現

設計者こそ「データ分析」が必要な理由

-

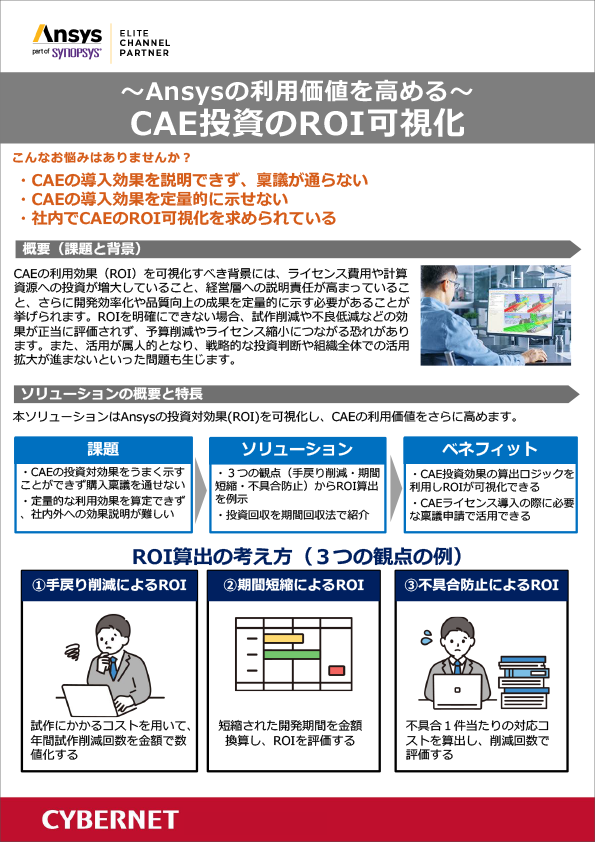

CAE投資のROI可視化でシミュレーションの利用価値を高める

-

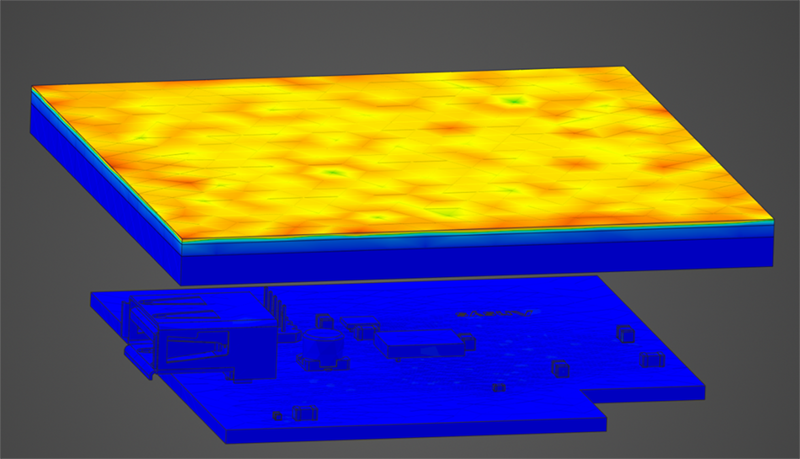

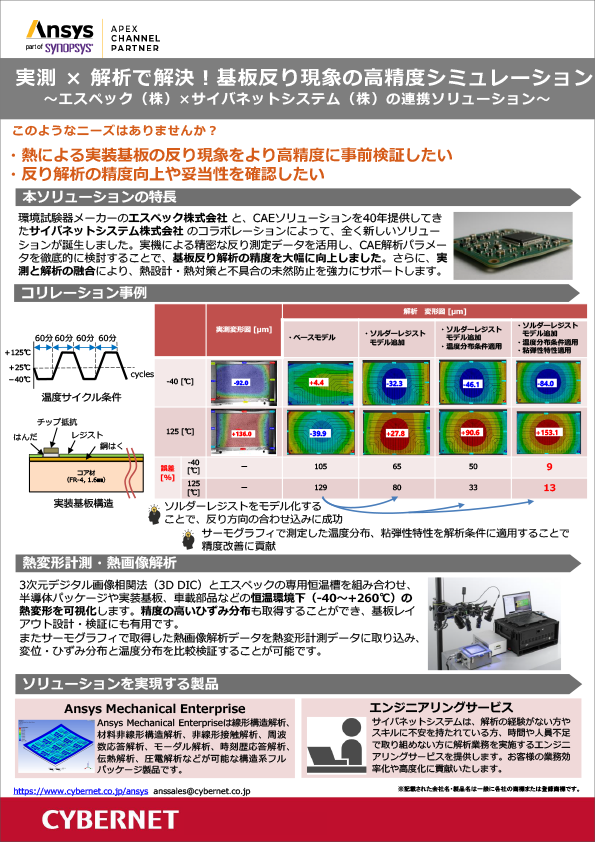

実測 × 解析で基板の熱変形問題を解決!基板反り現象の高精度シミュレーション

~エスペック(株)×サイバネットシステム(株)の連携ソリューション~

-

【全記事】CAEのあるものづくり vol.42

ユーザー様インタビュー記事7件を1冊に集約した保存版

-

誤差との上手なつきあい方 ~流体解析の計算誤差~ (完全保存版)

誤差との上手なつきあい方 前編・後編 を1冊にまとめた保存版 PDF

-

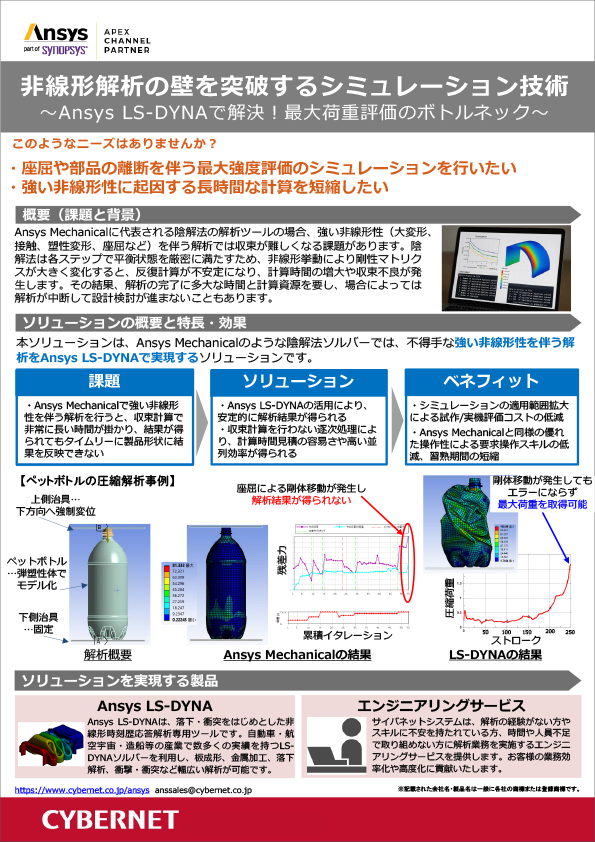

非線形解析の最大強度評価はAnsys LS-DYNAで解決!

~Ansys LS-DYNAで解決!最大荷重評価のボトルネック~