PCBパターン設計時の疑問を解消

電源プレーンはGNDプレーンより小さくすべき?

PCBパターン設計時の疑問を解消 :第1回

第1回 電源プレーンはGNDプレーンより小さくすべき?

第1回目は、「電源プレーンはGNDプレーンより小さくすべき?」というテーマです。

電源プレーンをGNDプレーンより小さくすることで、電源プレーン端からの電界のはみ出し(フリンジ電界)を抑えることができ、放射ノイズを低減することができると言われています。

しかし、「どれだけ小さくしたらよいか」というのは明確に示されていない場合も多く、一般論としては「絶縁層厚さの20倍」だけ小さくする※のが良いと言われています。(※20Hルールと呼ばれます。)

ただ、実際にレイアウトを行ってみると基板のサイズが小さい場合は「絶縁層厚さの20倍」というのが難しい場合もあります。

そこで今回は、そのような場合に電源プレーンのサイズをどのように設計すればよいか、3D電磁界シミュレータ「Ansys HFSS」を使って考えていきたいと思います。

使用する基板

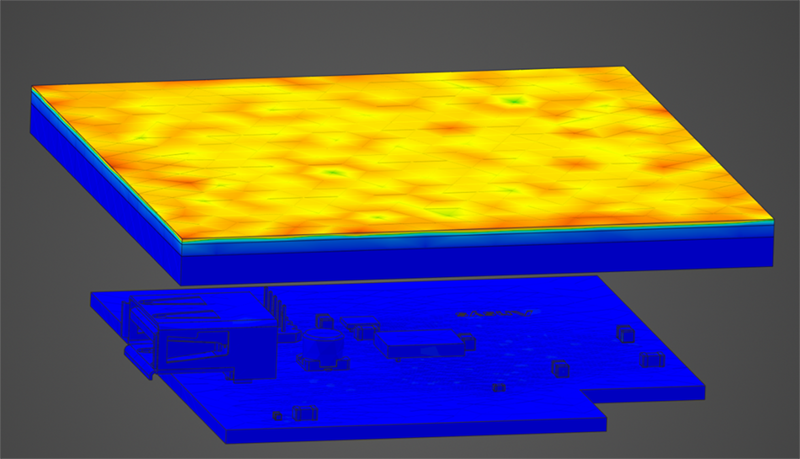

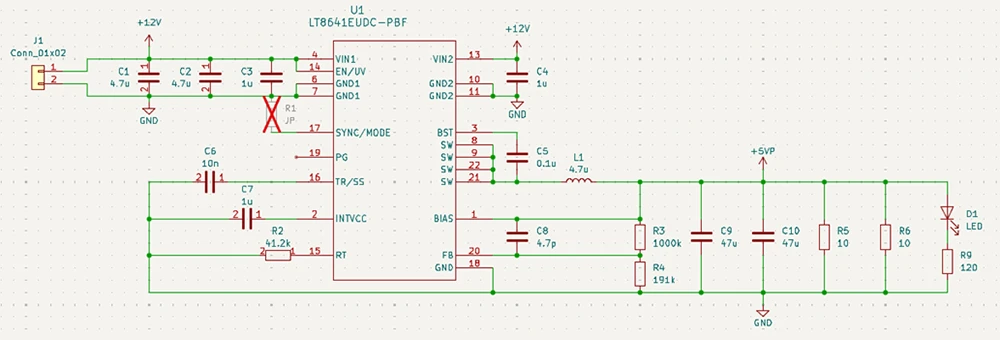

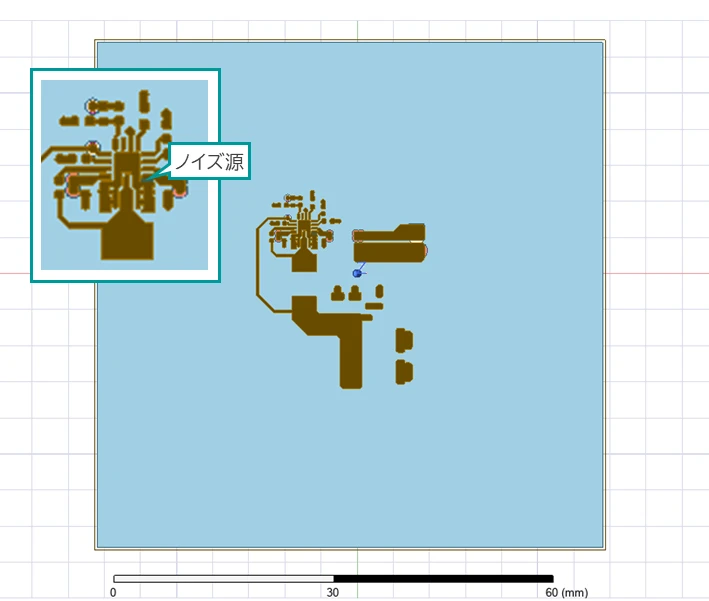

回路図をFig.1、レイアウトをFig.2に示します。

もっと単純化したモデルで解析しても良かったのですが、業務での使用をイメージしやすくするため、今回は実際の基板モデルを使用しています。

Fig.1 回路図

Fig.2 PCBレイアウト

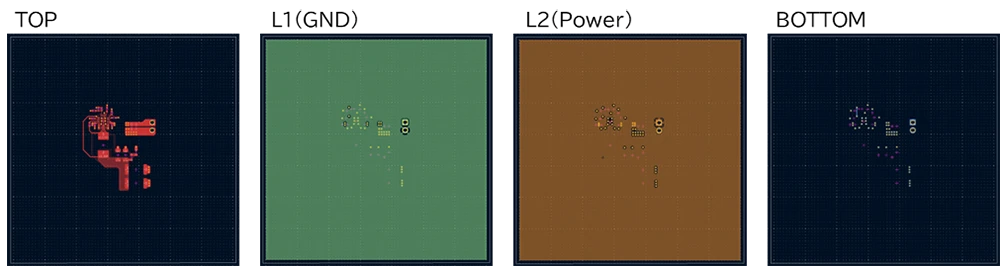

絶縁体厚さは1mmであり、20Hルールを検証するのに最大20mmのサイズ変更が可能な構成にしています。

解析条件 (GNDプレーンのサイズを変更した場合)

本来のルールとしては、GNDプレーンに対して電源プレーンのサイズを小さくするという内容なので、GNDプレーンのサイズをそのままにして電源プレーンのサイズを小さくして検証すべきです。

ただ、電源プレーンのサイズを小さくすると電源プレーンの共振特性が変わってしまい、GNDプレーンに対する電源プレーンのサイズの違いという本当に見たい部分(フリンジ電界の影響)が見えなくなってしまうのではないかと考えられます。

そこで、まずは電源プレーンサイズをそのままにしてGNDプレーン面積を大きくして解析してみようと思います。

評価は3m放射電界強度(30~1000MHz)によって行います。

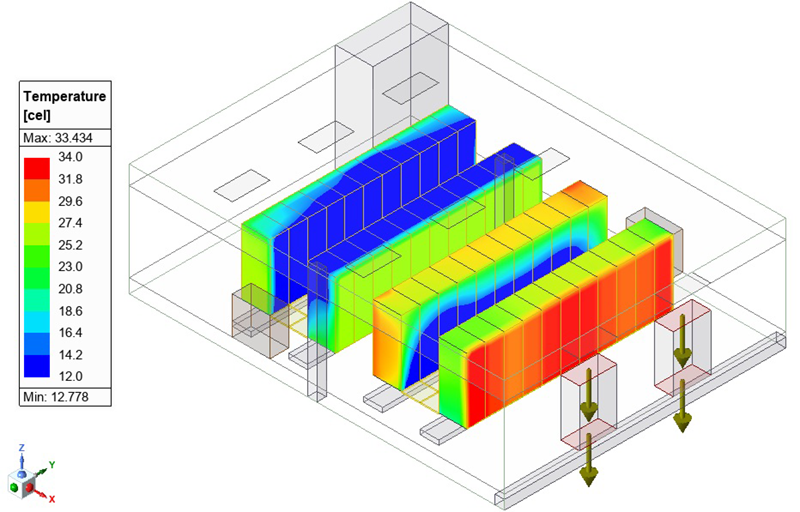

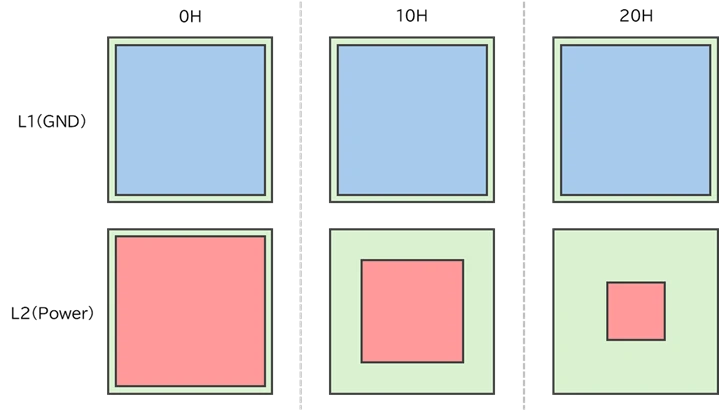

解析する基板の条件をFig.3に示します。

Fig.3 解析基板(GNDプレーンのサイズを変更)

- 0H: 電源プレーンとGNDプレーンのサイズが同じ

- 10H: 電源プレーンに対しGNDプレーンのサイズが10mm大きい

- 20H: 電源プレーンに対しGNDプレーンのサイズが20mm大きい

なお、ノイズ源は1V(30~1000MHz)とし、LT8641の電源入力ピンに設定します。(Fig.4)

Fig.4 解析モデルおよびノイズ源位置

解析結果 (GNDプレーンのサイズを変更した場合)

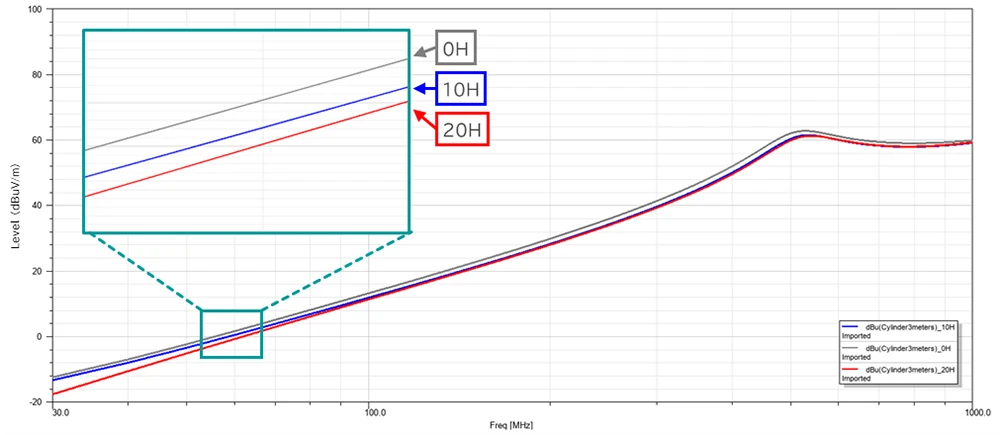

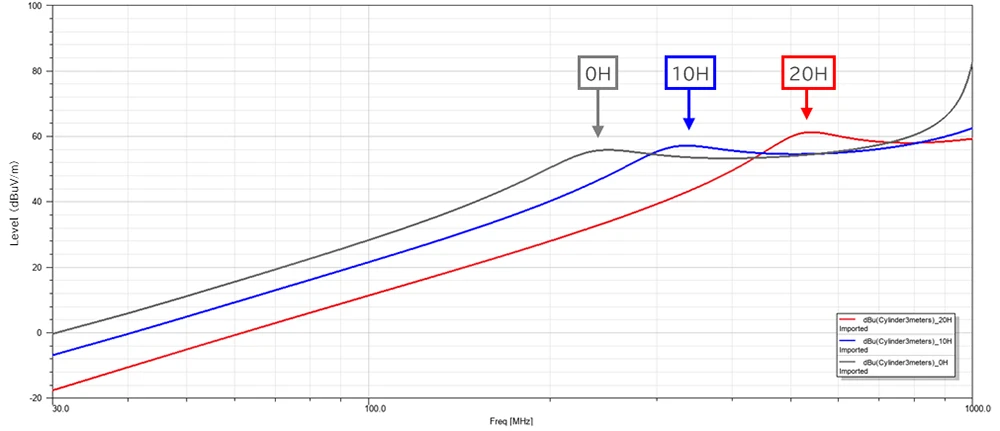

Fig.5 放射電界強度

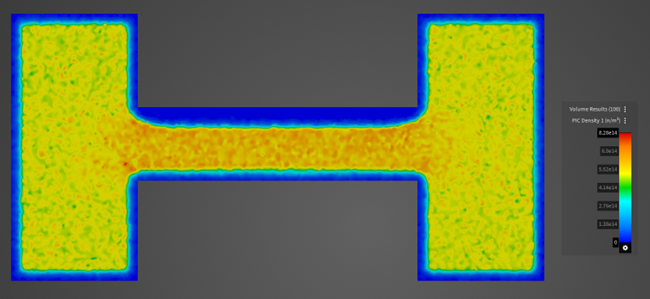

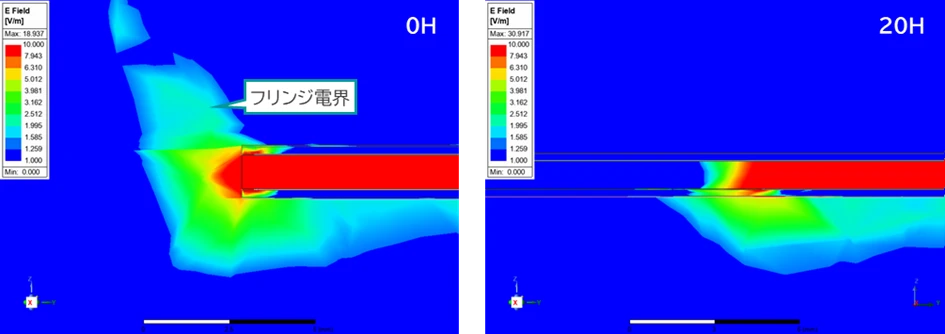

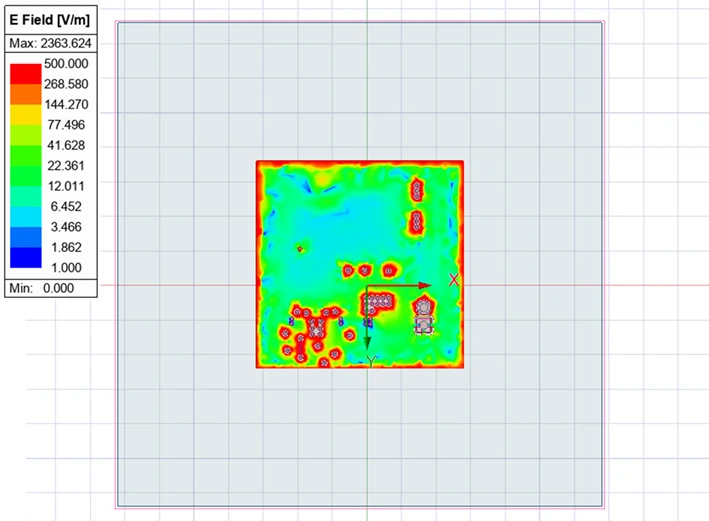

また、参考として「0H基板」と「20H基板」の電源プレーン端における電界分布を確認します。(Fig.6)

Fig.6 電界強度分布@30MHz

このように、「電源プレーンをGNDプレーンより小さくする」というのは放射ノイズを低減させるためのルールとして一定の効果があることがわかります。

ただ、Fig.5の結果からわかるように、GNDプレーンを20mm大きくしても放射電界強度は1~2dBuV/m程度しか低減せず、効果としてはそこまで大きなものではありませんでした。

そのため、わざわざGND面積を大きくする、つまり基板サイズを大きくしてまで実施する必要があるのかどうかは疑問が残ります。

そこで、次は本来のルールに沿って、GNDプレーンのサイズは変えずに電源プレーンのサイズを小さくしていき解析を行っていきたいと思います。

解析条件 (電源プレーンのサイズを変更した場合)

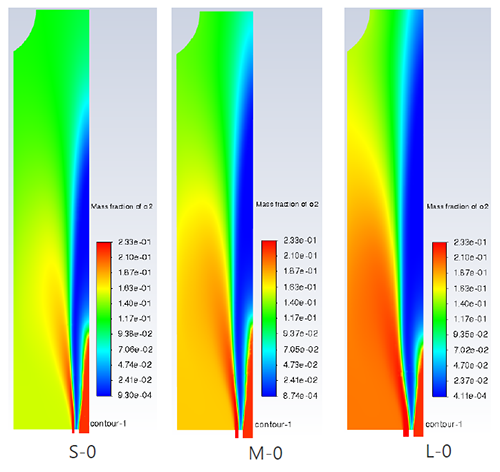

解析する基板の条件をFig.7に示します。

20Hの条件はGNDプレーンのサイズを変更した場合と同じになります。

Fig.7 解析基板(電源プレーンのサイズを変更)

- 0H: GNDプレーンと電源プレーンのサイズが同じ

- 10H: GNDプレーンに対し電源プレーンのサイズが10mm小さい

- 20H: GNDプレーンに対し電源プレーンのサイズが20mm小さい

なお、ノイズ源の設定はGNDプレーンのサイズを変更した場合と同様です。

解析結果 (電源プレーンのサイズを変更した場合)

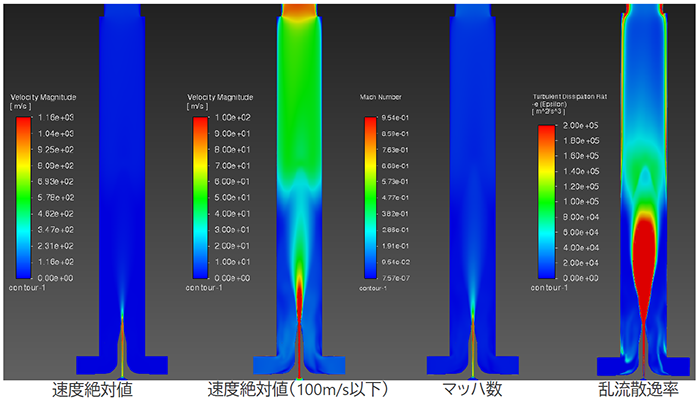

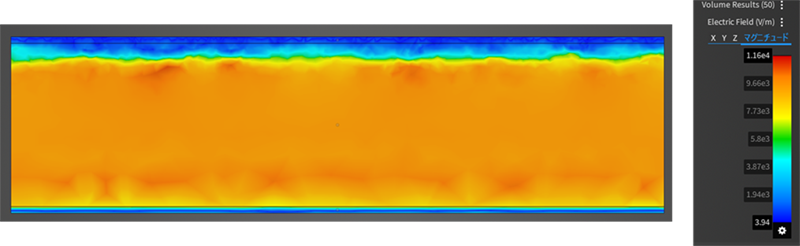

Fig.8 3m放射電界強度

また、GNDプレーンに対して電源プレーンを10mm小さくするごとに放射電界強度が約8~10dBuV/mずつ低減していることが確認でき、GNDプレーンサイズのみ変更した場合(Fig.5)と比較して効果が大きいことが確認できます。

ただし、やはりGNDプレーンに対してのサイズというよりは、電源プレーンそのもののサイズ違いによって共振周波数がずれていっているだけのようにも見えます。

このことから、「電源プレーンをGNDプレーンより小さくする」というルールに関しては、フリンジ電界の低減ももちろん期待できますが、最終的な放射電界強度への影響としては電源プレーンが小さくなったことによる共振周波数のシフトの方が支配的になっていると考えられます。

それでは、「どれだけ小さくしたらよいか」という本コラムの当初の疑問に対する回答としては、「電源プレーンを可能な限り小さくする」ということになるのでしょうか?

どう設計すればよいか?

これまでの解析内容で、以下のことがわかりました。

今回の解析条件下において:

- GNDプレーンを大きくすると、フリンジ電界が抑制され広帯域で放射電界強度がわずかに低下

- 電源プレーンを小さくすると、共振周波数が高周波側へ移動し低周波帯の放射電界強度が低下

- ただし、フリンジ電界抑制よりも共振周波数シフトの影響が支配的

上記を踏まえると、一般的には「GNDプレーンは可能な限り大きくし、電源プレーンは可能な限り小さくする」というのが、フリンジ電界の抑制効果と共振周波数のシフトによる効果を両取りできる基本的な設計指針になるように思えます。

しかし、気を付けなければならない点が一点あります。

それは、共振周波数はシフトしているだけで共振によるピークが消えるわけではないという点です。

Fig.8を見ると20H基板が最も放射電界強度が低く良い結果のように見えますが、420~700MHzにおいては共振によって放射電界強度が他の条件よりも高くなっていることが確認できます。

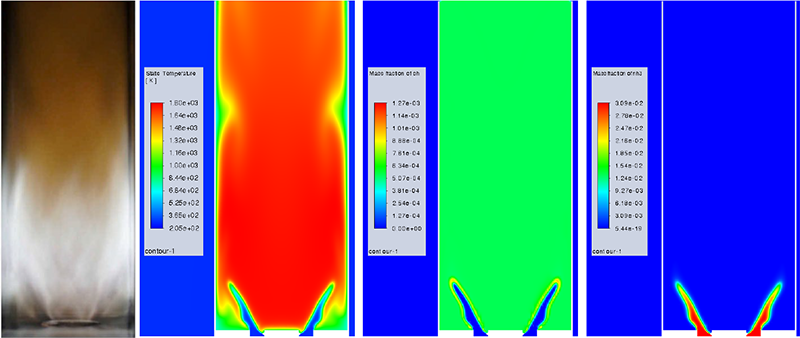

それでは、20H基板で放射電界強度が最も高い530MHzにおける電界強度分布を確認してみます。(Fig.9)

Fig.9 放射電界強度@530MHz (20H基板)

よって、もし基板内に420~700MHzのノイズが存在していた場合、電源プレーン自体がパッチアンテナのように作用しノイズを効率よく放射してしまい、0~15H基板よりも放射電界強度が高くなってしまう可能性があります。

このように、ルールを守るだけでは十分な効果が得られない、または逆効果になってしまう場合があります。

そのため、今回のようにシミュレーションを実施し、ルールを守るだけではなくしきれないリスクを確認することが大切です。

結論

電源プレーンとGNDプレーンのサイズに関して、今回の基板においては以下の結論が得られました。

- 電源プレーンよりもGNDプレーンを大きくすると広い周波数帯域で放射電界強度が下がる

ただし、大きな効果は得られない可能性がある - 電源プレーンを小さくすると低い周波数帯域で放射電界強度が低減する傾向がある

ただし、共振周波数がシフトするため別の周波数帯で放射が増える可能性もある。 - ルールを守ることで問題が起きる可能性を下げることはできるがリスクを完全になくすことはできない。

➡ リスクを最小限にするためにはシミュレーションの活用が重要である。

なお、この結論はあくまで今回解析した基板にもとづくものであり、基板サイズや形状が異なれば別の問題が発生する可能性もあります。

このように、昔自分が言われた「シミュレーションしてみないとわからない」というのが結論になってしまうのは少し心苦しいですが、シミュレーションをどのように活用すればよいかを考えるうえで、本コラムの内容が一つの参考になれば幸いです。

なお、今回の解析は「Ansys HFSS」を使用して実施しましたが、共振解析であれば冒頭でも触れた「DEMITASNX」でも実施が可能です。

これからもPCBパターン設計時の疑問をシミュレーションによって解消していきたいと思いますので、もし興味があればチェックしてみてください。

また、「こんなときどうすればいいの?」といった疑問があれば、ぜひお気軽に以下のボタンからお問い合わせください。

EMCのことならサイバネットにお任せください

サイバネットは、お客様のEMCに関するお悩みをトータルで解決いたします。

「なにから始めればよいかわからない」

そんなときこそ、まずはサイバネットに相談してみませんか?

ご相談・お見積りは無料です。

関連記事

関連情報

関連する解析事例

MORE関連する資料ダウンロード

MORE-

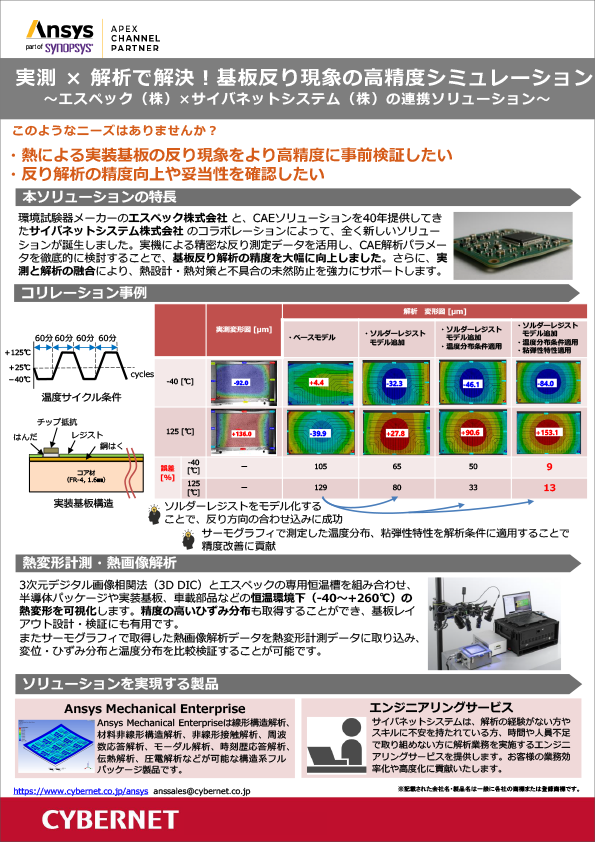

実測 × 解析で基板の熱変形問題を解決!基板反り現象の高精度シミュレーション

~エスペック(株)×サイバネットシステム(株)の連携ソリューション~

-

【全記事】CAEのあるものづくり vol.42

ユーザー様インタビュー記事7件を1冊に集約した保存版

-

誤差との上手なつきあい方 ~流体解析の計算誤差~ (完全保存版)

誤差との上手なつきあい方 前編・後編 を1冊にまとめた保存版 PDF

-

非線形解析の最大強度評価はAnsys LS-DYNAで解決!

~Ansys LS-DYNAで解決!最大荷重評価のボトルネック~

-

事例でご紹介!流体解析分野のエンジニアリングサービス ~解析業務の委託・立ち上げ支援・カスタマイズによる効率化など~

-

はんだ濡れ上がり形状予測解析で電子機器の信頼性向上

~Ansys LS-DYNAで電子機器の信頼性向上に貢献~

-

Ansys ユーザーのための PyAnsys 完全ガイド

Pythonで加速するCAEワークフロー

-

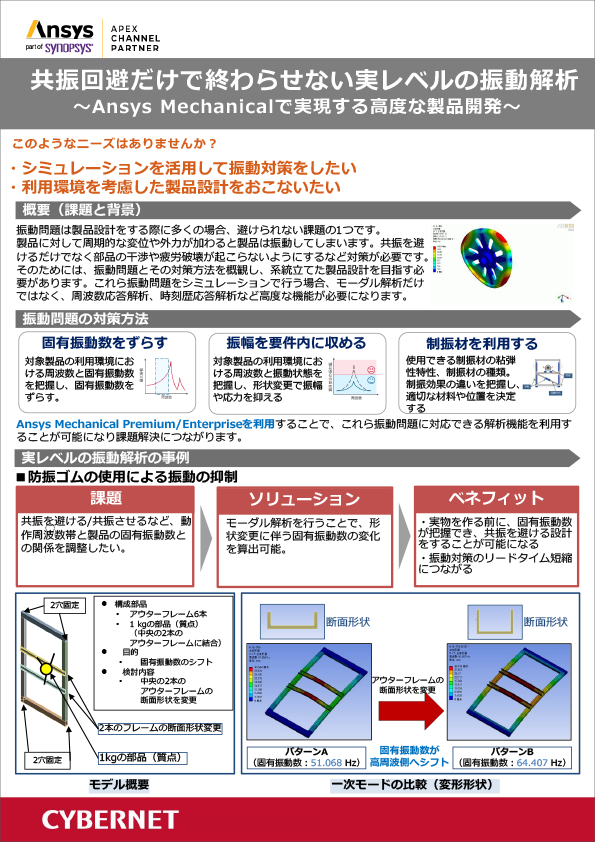

共振回避だけで終わらせない振動解析の進め方を解説(周波数応答・時刻歴まで)

~Ansys Mechanicalで実現する高度な製品開発~