CAEを学ぶ

IBISモデル(あいびすもでる)

英訳:IBIS Model

1.IBISモデルとは

IBIS=Input/Output Buffer Information Specification の略で、デジタル回路の伝送線路解析(シグナルインテグリティ)のために、デバイスをアナログ ビヘイビア(動作記述)モデルにしたものを指します。 簡単に言えば、『 プリント基板設計のためのシミュレーションモデル 』です。

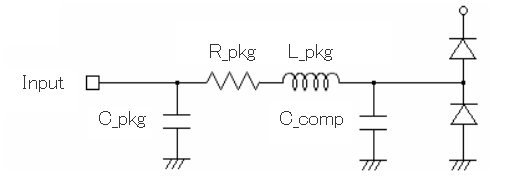

IBISの規格は、IBISオープンフォーラムが策定したものですが、情報のフォーマットを想定しただけで、シミュレータでの処理やモデルの使用方法については、特に指定されていません。 IBISモデルは、デバイスのピンのアサイン情報や入出力の仕様を記述した単純なもので、基本的な構成は、下のようなものです。

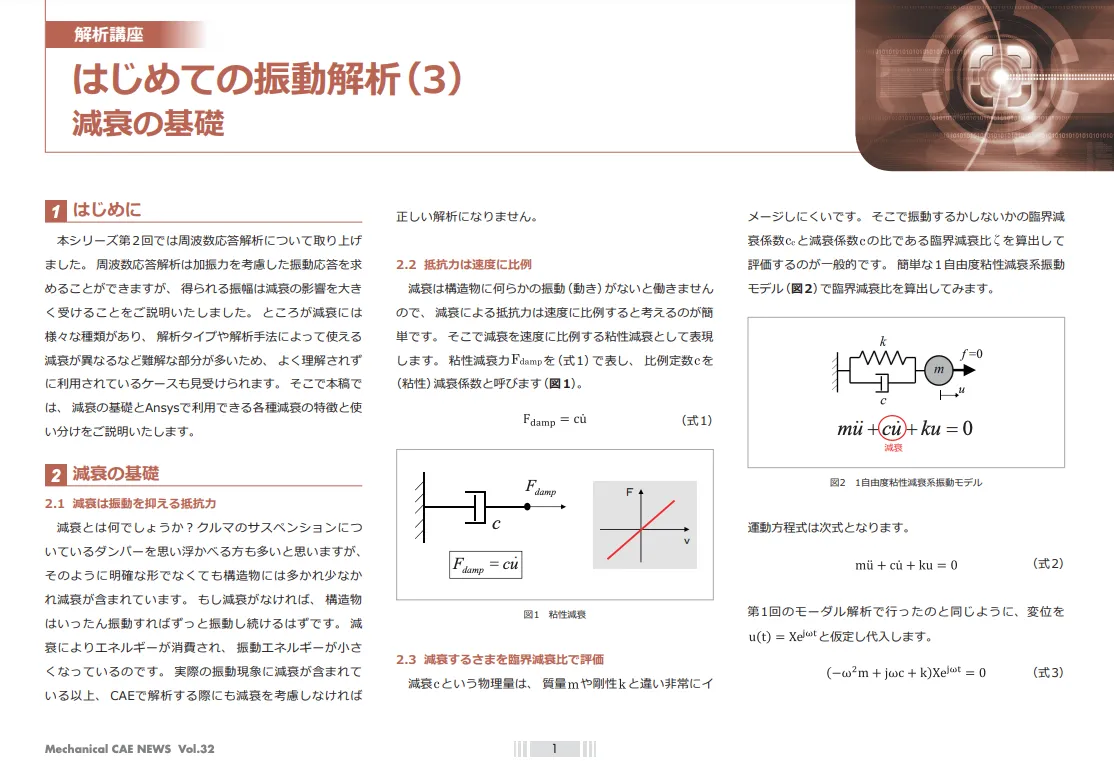

1-1. ドライバモデル(出力モデル)

- スルーレート:立ち上がり、立ち下りの特性

- プルダウン I-V カーブ:ロー側トランジスタの電流 - 電圧特性

- プルアップ I-V カーブ:ハイ側トランジスタの電流 - 電圧特性

- I-Vカーブ:電源側クランプダイオードとグランド側クランプダイオード特性

- 半導体チップ(ダイ)のキャパシタンス

- パッケージのLCR

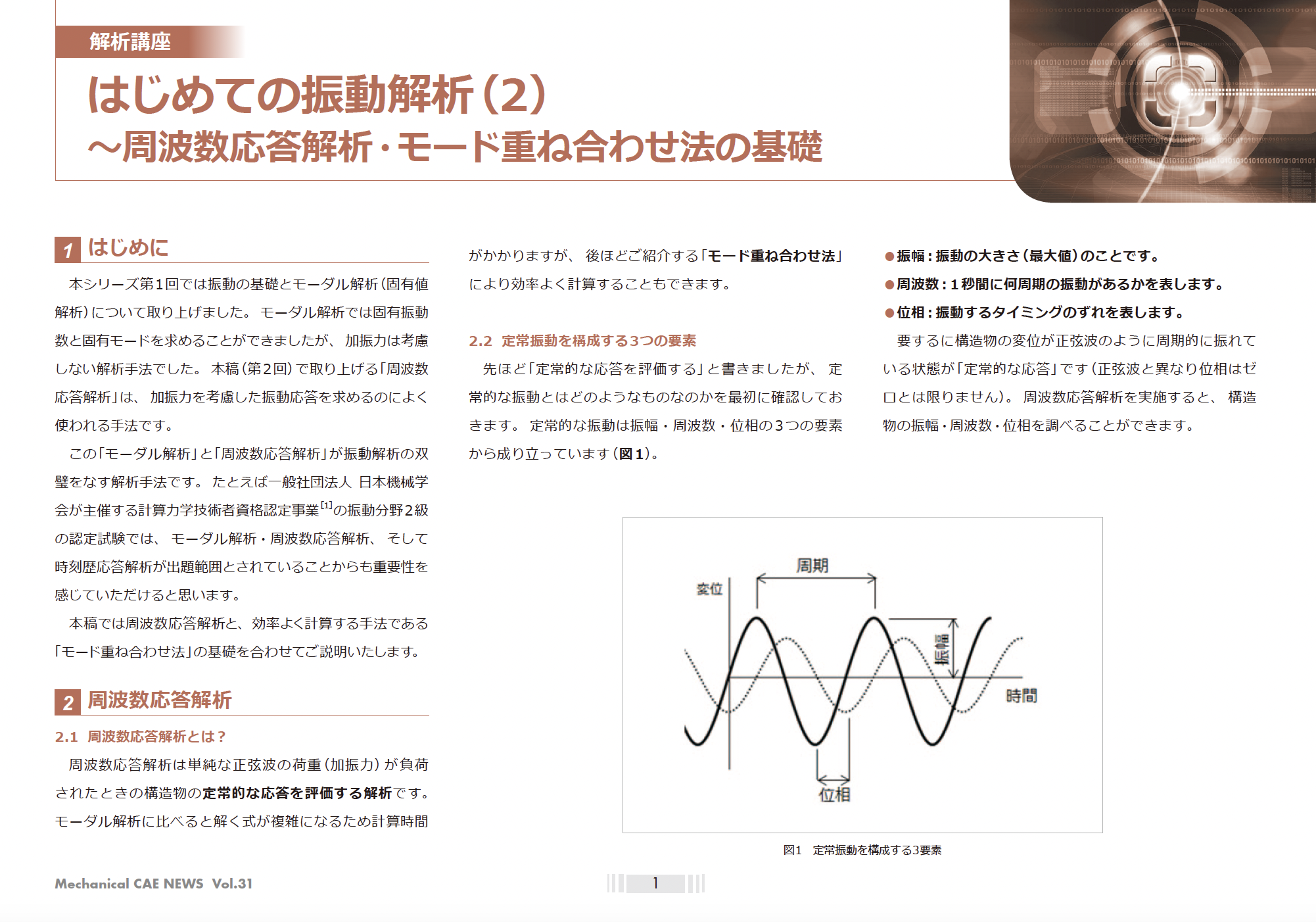

1-2. レシーバモデル(入力モデル)

- I-Vカーブ:電源側クランプダイオードとグランド側クランプダイオード特性

- 半導体チップ(ダイ)のキャパシタンス

- パッケージのLCR

また、IBISモデルは伝送線路解析に特化しているため、そのシミュレーション時間はSPICEモデルの10倍も高速と言われており、これが世界中でIBISモデルが使われている大きな理由の一つとなっています。

2. IBISモデルの重要性

近年、IC・半導体の高速化・高集積化に伴い、プリント基板設計はもとより回路設計の段階から伝送線路の解析(最適な部品配置など)が求められています。 その解析に必要な素子モデルとして、IBISモデルとSPICEモデルが広く利用されていますが、簡便性、入手性、処理時間、効率性などの理由により、IBISモデルが適しています。

しかしながら、入手可能なIBISモデルの多くは、編集作業を前提としていたり、シミュレータとの整合性や、記述上の問題を含んでいるのが現実です。 では、IBISモデルに問題がある場合、お客様にどのような不都合が生じるのでしょうか。

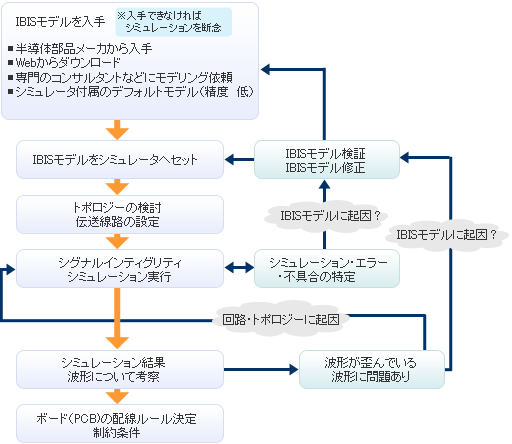

上の図は、プリント基板を設計・解析するための一般的な過程を表しています。

半導体や受動部品を実装しているプリント基板の設計において、試作回数の低減、後戻り工数を軽減させるためには、ツールを用いたシグナルインテグリティ解析は不可欠です。

しかし、実装するデバイスのIBISモデルに問題があれば、シミュレーション途中でエラーが生じ、何度もエラー原因の究明やIBISモデルの修正を加える工程が増え、時間と工数が増えてしまいます。

また、スムーズに解析できたとしても、問題のあるIBISモデルで解析してしまった場合、試作品の実測値とシミュレーション結果が合わず、想定外のプリント基板ができてしまい、試作品数や工数は低減されずに結果として生産コストに影響が出てしまいます。

これでは、何のためにシミュレーションしているのか分りません。

IBISモデルは、プリント基板のシミュレーション精度や工程に大きな影響を及ぼすだけではなく、お客様のコストにも 大きく関与している重要なデータなのです。

CAE用語辞典の転載・複製・引用・リンクなどについては、「著作権についてのお願い」をご確認ください。

関連情報

関連する解析事例

MORE関連する資料ダウンロード

MORE-

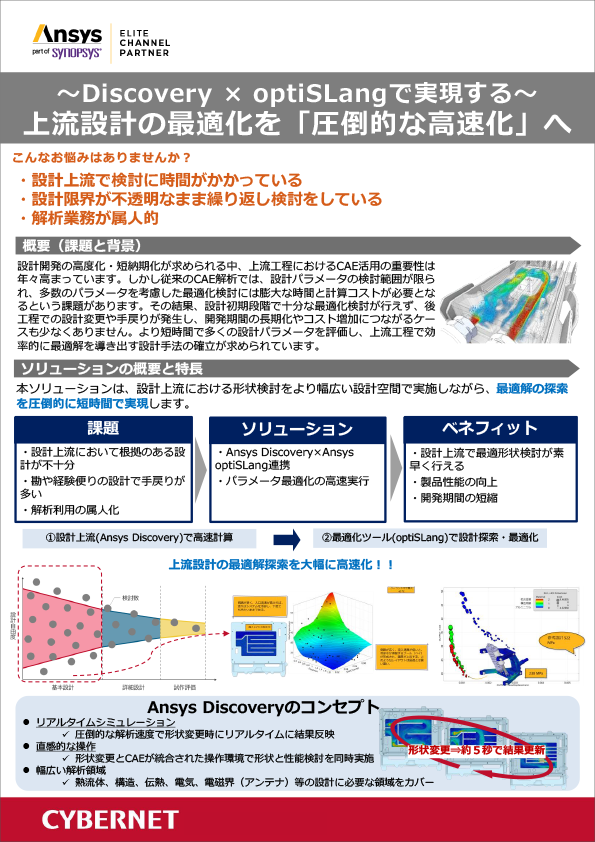

短時間で設計パラメータを評価。上流設計の最適化を「圧倒的な高速化」へ

設計上流における形状検討をより幅広い設計空間で実施

-

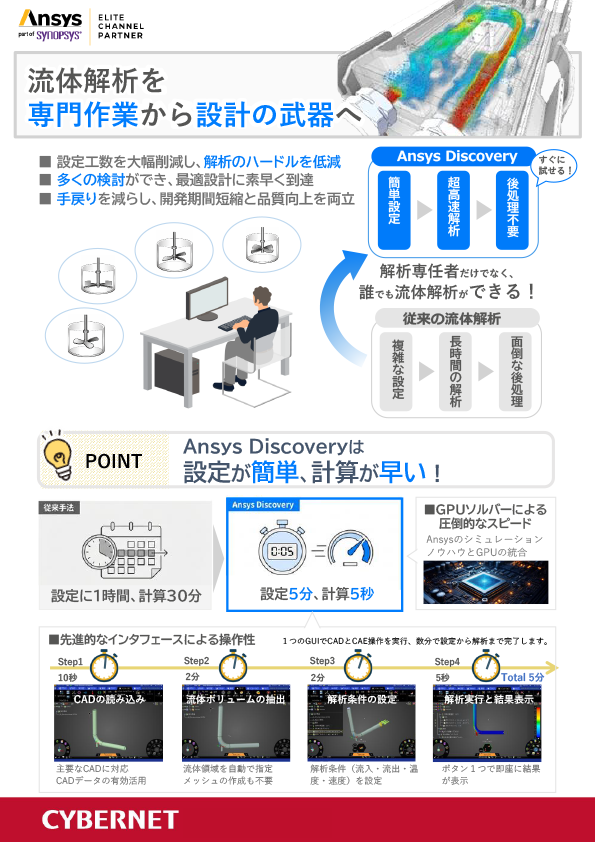

解析専任者だけでなく誰でも解析ができる!設計者のための超高速リアルタイム解析

流体解析を専門作業から設計の武器へ

-

物理状態と統計データの可視化で意思決定の高速化を実現

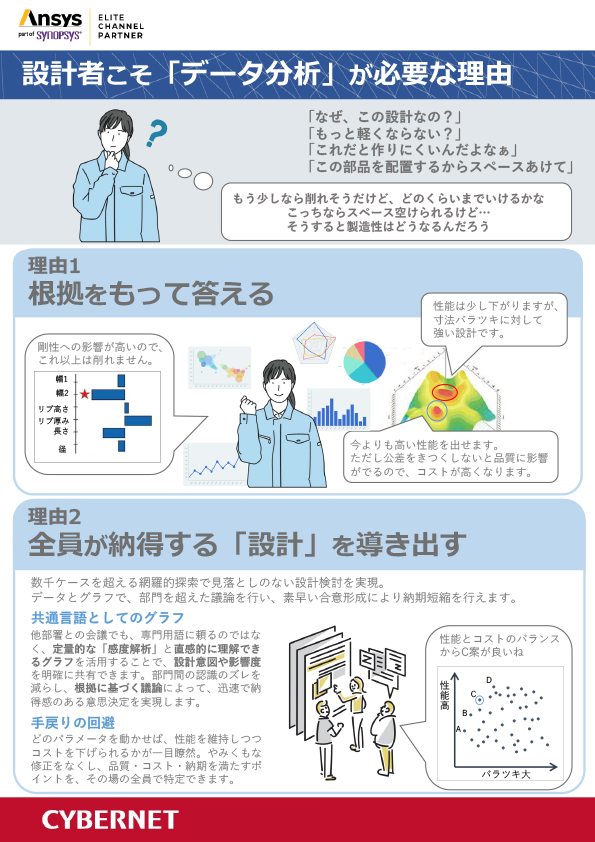

設計者こそ「データ分析」が必要な理由

-

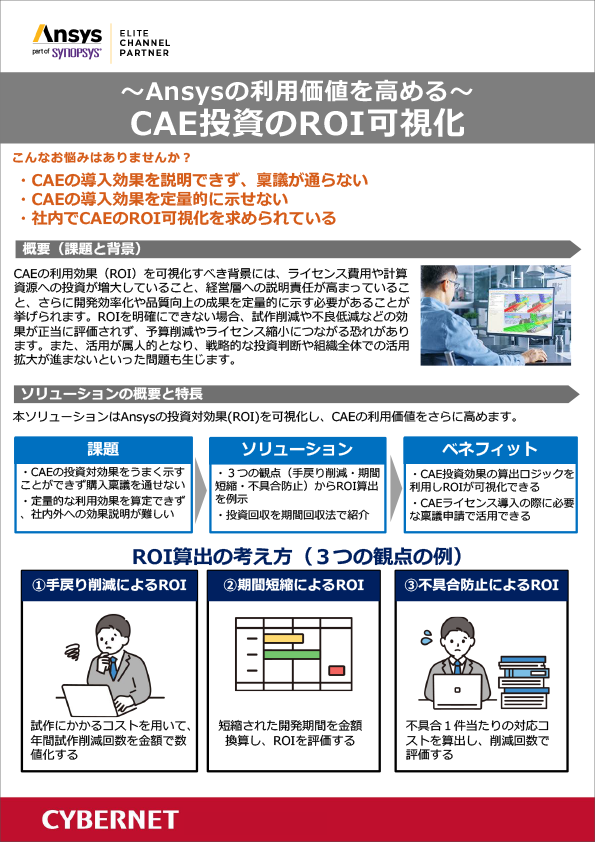

CAE投資のROI可視化でシミュレーションの利用価値を高める

-

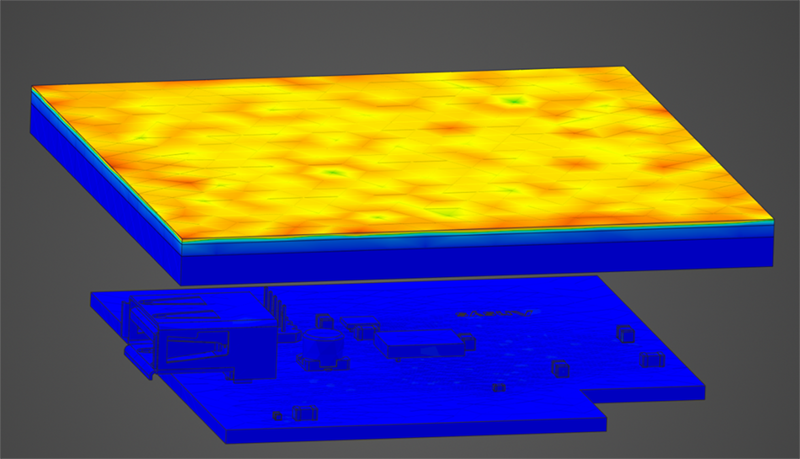

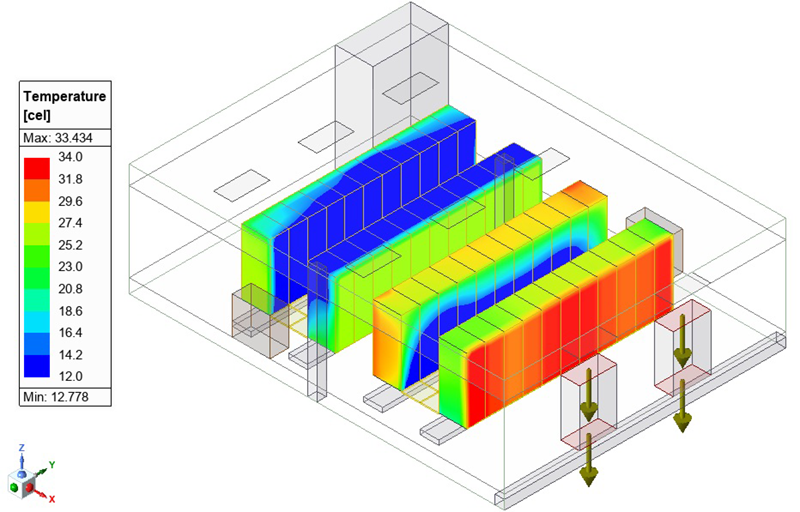

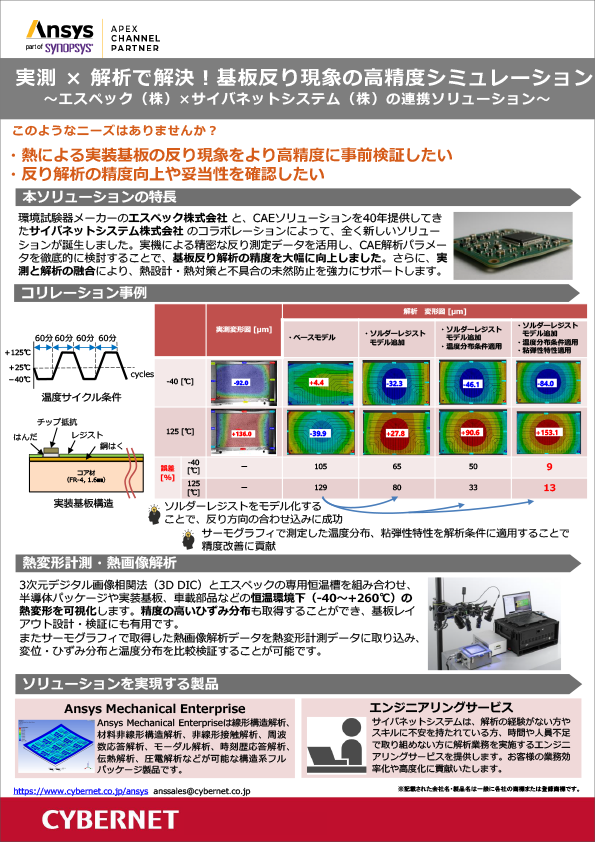

実測 × 解析で基板の熱変形問題を解決!基板反り現象の高精度シミュレーション

~エスペック(株)×サイバネットシステム(株)の連携ソリューション~

-

【全記事】CAEのあるものづくり vol.42

ユーザー様インタビュー記事7件を1冊に集約した保存版

-

誤差との上手なつきあい方 ~流体解析の計算誤差~ (完全保存版)

誤差との上手なつきあい方 前編・後編 を1冊にまとめた保存版 PDF

-

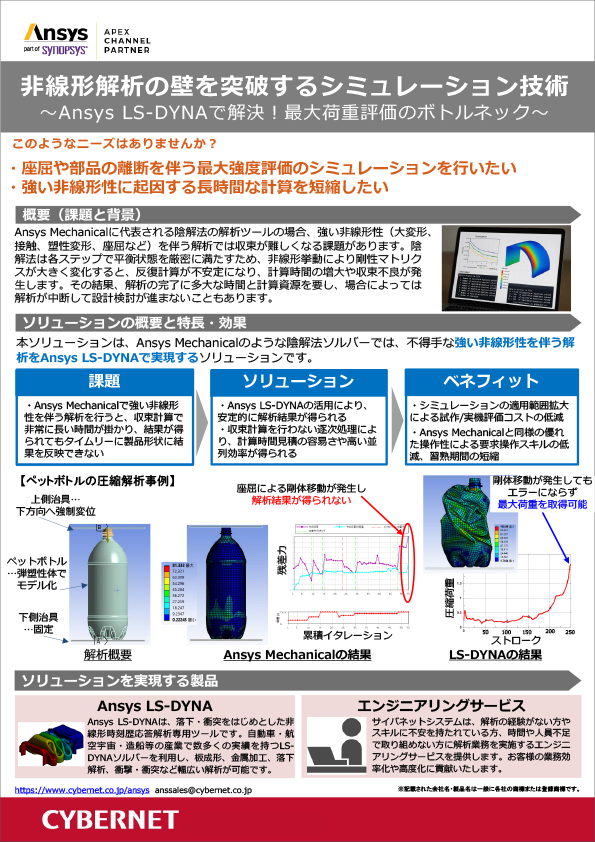

非線形解析の最大強度評価はAnsys LS-DYNAで解決!

~Ansys LS-DYNAで解決!最大荷重評価のボトルネック~