EMC規格の意図や関係性を知れば、ノイズ設計に強くなる!

ESD規格の内容と考え方を知ろう!

EMC規格の意図や関係性を知れば、ノイズ設計に強くなる! :第3回

第3回 ESD規格の内容と考え方を知ろう!

EMCの規格にはEMI(周りに電磁的影響を与えない)という要求とEMS(周りから電磁的影響を受けない)という要求の2つに分けられます。

第3回はこのEMSの一つである静電気放電(ESD)の規格についてお話します。

ESD規格にも製品群規格や製品規格など様々ありますが、試験方法やセットアップについては多くがIEC 61000-4-2を参照しています。

今回は、IEC 61000-4-2の内容と、ESD対策の基本的な考え方について解説していきたいと思います。

IEC 61000-4-2について

試験としてはESD発生器(ESDガン)を用いてESDを模擬した放電を印加することで評価を行います。

ESD発生器では充電用のコンデンサ(一般的には150pF)に電荷を蓄え、放電スイッチをONした際に放電抵抗(一般的には330Ω)を介して機器に放電することによりESD放電が模擬されます。

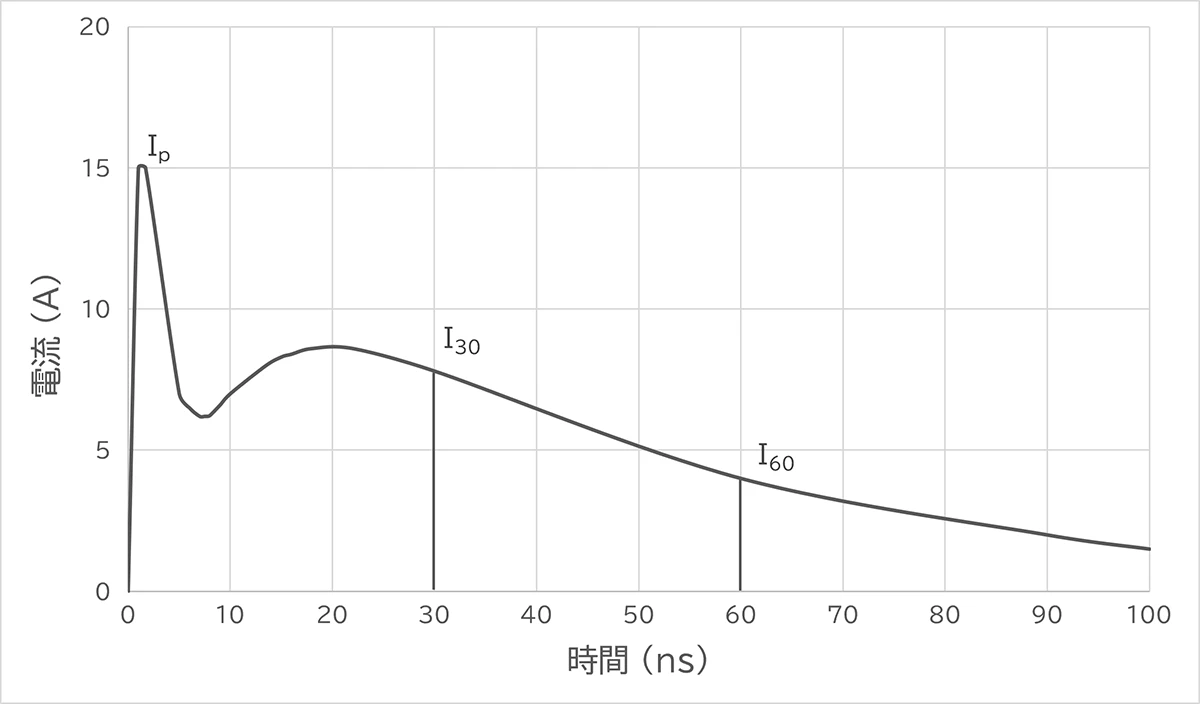

また、接触放電電流は以下の波形のように、立ち上がり時間、ピーク電流、30ns後及び60ns後の電流値で定義されます。

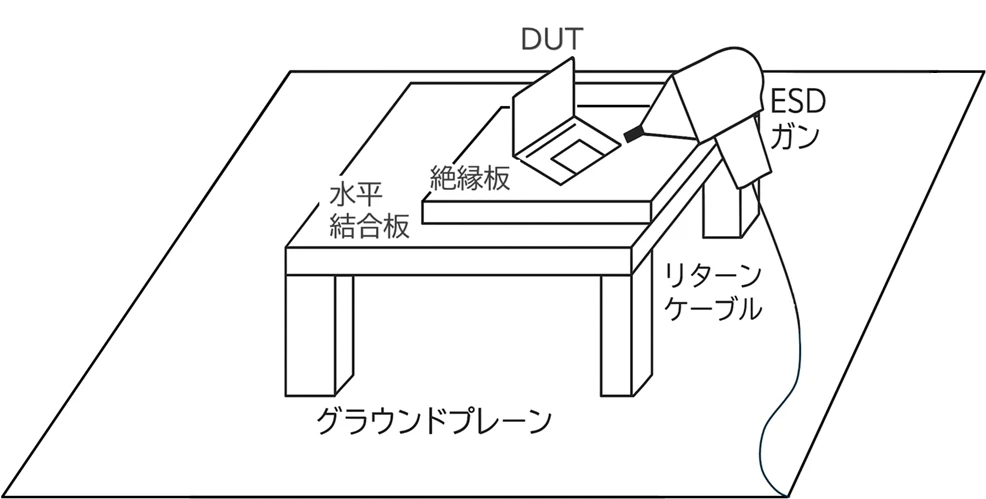

試験セットアップは、以下の条件で配置されます。

- シールドルーム等の外部ノイズが遮断されかつグラウンドプレーンが配置された試験室内

- 製品の使用条件に応じて非導電性のテーブル上または床置き

- 机上の場合テーブル上に水平結合板を設置し、抵抗(470kΩx2)とケーブルを介してグラウンドプレーンに接続

- 製品の実際の使用条件で電源、通信ケーブルを接続

- 試験対象の機器及び接続ケーブルは絶縁板によってグラウンドプレーン、水平結合板から絶縁

- ESD発生器のリターンケーブルはグラウンドプレーンに接続

机上試験でのセットアップ例は以下のようになります。

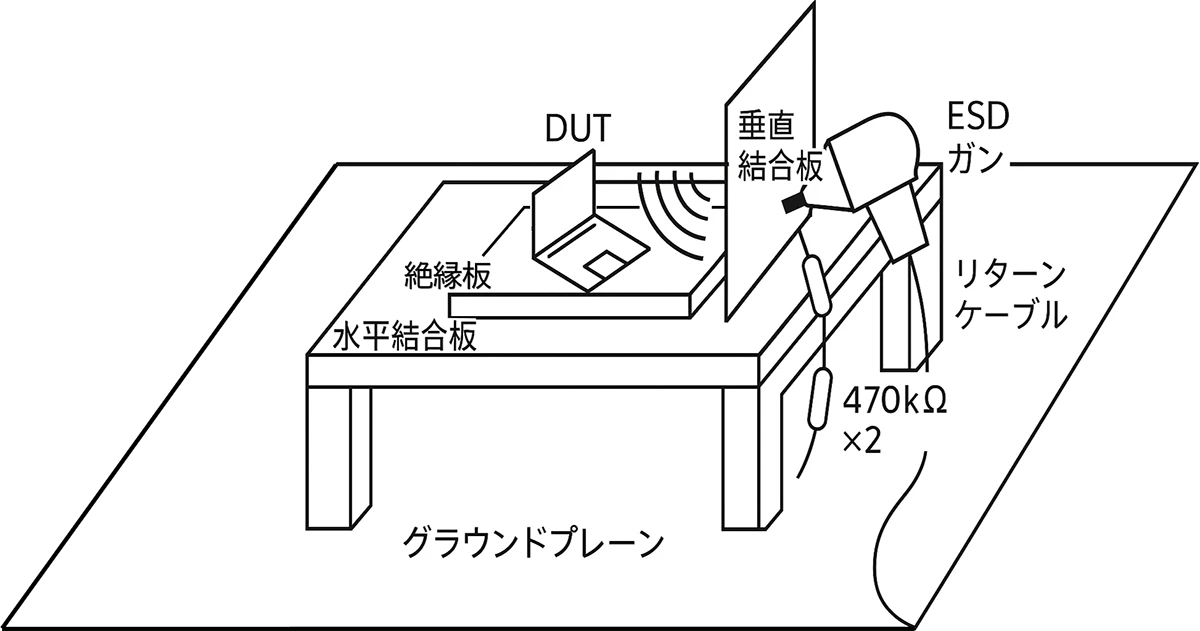

直接放電は機器への直接の放電、間接放電は周辺機器や金属への放電による間接的な影響を想定しています。

直接放電の場合はESD発生器から機器に放電を行いますが、間接放電の場合は水平結合板または垂直結合板に対して放電を行い、それによって発生する電磁波によるイミュニティ影響を確認します。水平結合板、垂直結合板は放電間隔で十分に放電でき、かつ即座に除電されないようにグラウンドプレーンとの間に(470kΩx2)の抵抗を介して接続されます。

間接放電のイメージは以下のようになります。

ESD設計の考え方

ESDに対する設計、対策は大きく分けて以下の2つの考え方があります。

- ノイズの流入を防止する

- ノイズが流入した場合の誤動作・破壊を防止する

1つ目のノイズの流入を防止する場合にも2種類の考え方があります。

まず、「ESDが内部に侵入しないように筐体設計を行う」という考え方です。

例えば、製品をグラウンド接続されたシールド筐体で覆い、かつ侵入を防ぐべき箇所(基板など)との間の絶縁距離を確保することで、内部へのESDの直接的な侵入を防止することができます。

樹脂筐体の場合にも、ESDが侵入する可能性のある開口部や隙間から絶縁距離を確保することで同様に内部への侵入を防止できます。

ただし、外部コネクタ等のインターフェース部分はこういった考え方での侵入防止には限界があります。

こういった部分へはもう一つの「ESDが侵入した場合に保護すべき箇所にノイズを流入させない」という考え方が重要になります。

例えば、静電気の侵入が想定される個所に筐体との接続を設けることで静電気を逃がす経路を作り、かつフィルタ部品を追加することでIC部品等の保護すべき箇所へのノイズ影響を防止することができます。

この考え方は無線周波妨害の伝導イミュニティとも一部共通した考え方になります。

2つ目のノイズが流入した場合の誤動作・破壊を防止する対策には、保護すべき端子の近傍にバリスタやTVSダイオードといったクランプ素子やチップコンデンサを配置するという方法があります。

チップコンデンサは高周波のインピーダンスが低いため、保護すべきICの端子に高周波電流が流れることを防止することが出来ますが、ノイズのエネルギーが大きいような場合にはコンデンサ自身の定格を超過し破壊が発生する場合があることに注意が必要です。

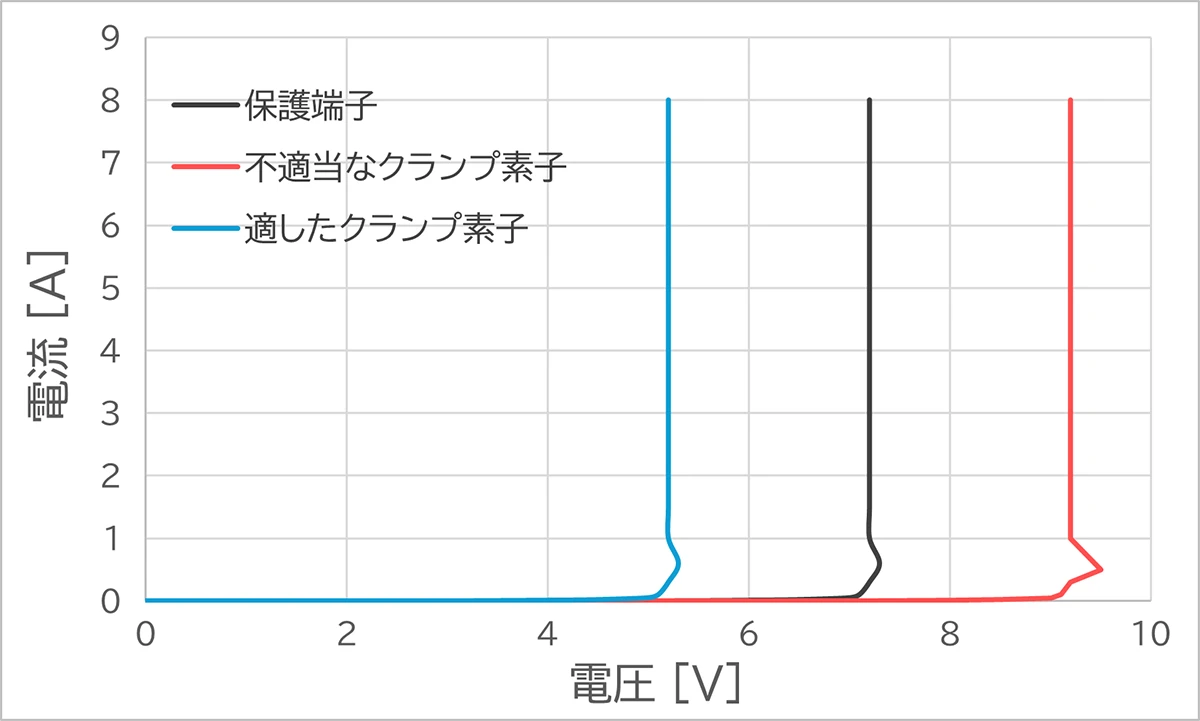

クランプ素子は非線形特性を持つ素子で、一定電圧以上で流れる電流量が急激に増加することで、保護すべき端子に耐圧以上の電圧がかかることを防止します。

ここで注意すべき点は、クランプ素子の応答速度とI-V特性です。

ESDは瞬時的かつ大きなエネルギーであるため、応答速度の遅い素子では保護素子として十分に働かない可能性があります。

また、ICの端子内部にも過電圧を防止するために保護素子が含まれている場合があります。このような場合には内部の保護素子とESD保護として配置されるクランプ素子のI-V特性の関係によっては、優先的に内部の保護素子に電流が流れてしまうことがあります。一般的に内部の保護素子は外部に配置されるクランプ素子よりも許容電流量が小さいため、こういった設計により端子破壊が発生する場合があります。

このようなI-V特性の確認にはTLP測定が有効です。

TLP測定では、ESDのような短い時間のパルス波に対する端子や部品のI-V特性を確認できます。

この測定によって、保護対象の端子とクランプ素子の特性を事前に把握することができるため、このようなI-V特性の不適合による設計問題を未然に防ぐことが可能です。

このように、設計において考慮すべき要素を整理することで、共通する要素を把握しEMC全体の設計として効率的な設計・対策を実施することが可能となります。

まとめ

瞬時的なノイズとなるため特有の部分もありますが、放射イミュニティや無線周波妨害の伝導イミュニティと共通する点もあることが理解していただけたかと思います。

効率的なEMC設計を行う上でこういった考え方が重要になりますので、ご自身で考えるきっかけとなれば嬉しく思います。

関連情報

関連する解析事例

MORE関連する資料ダウンロード

MORE-

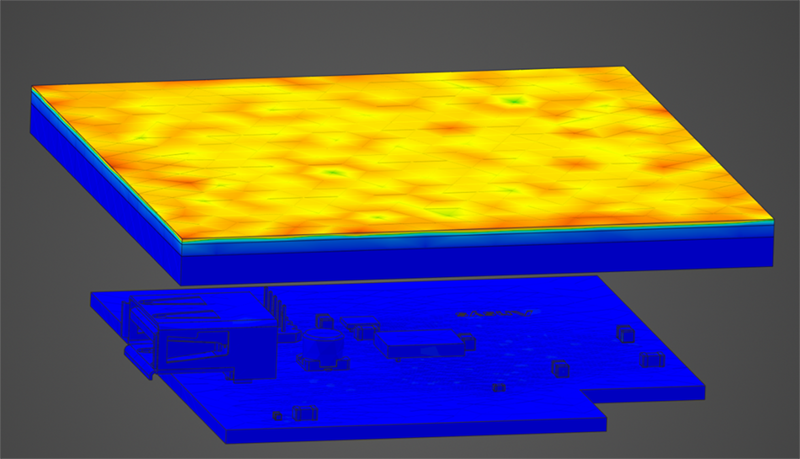

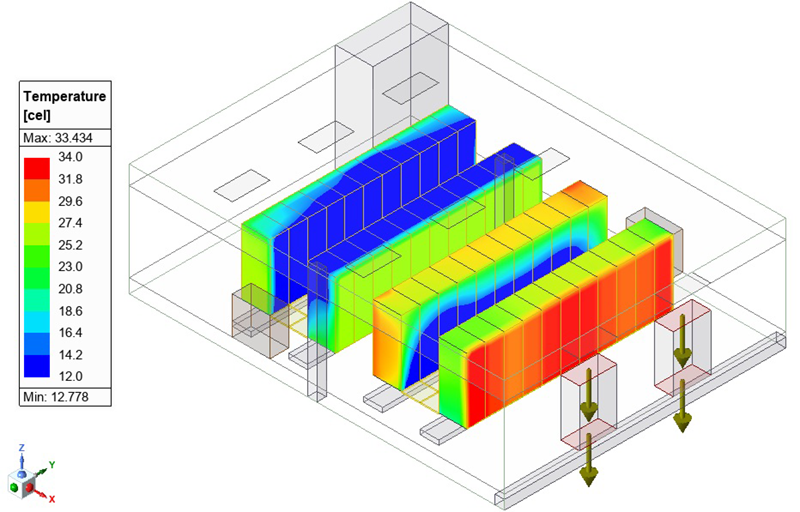

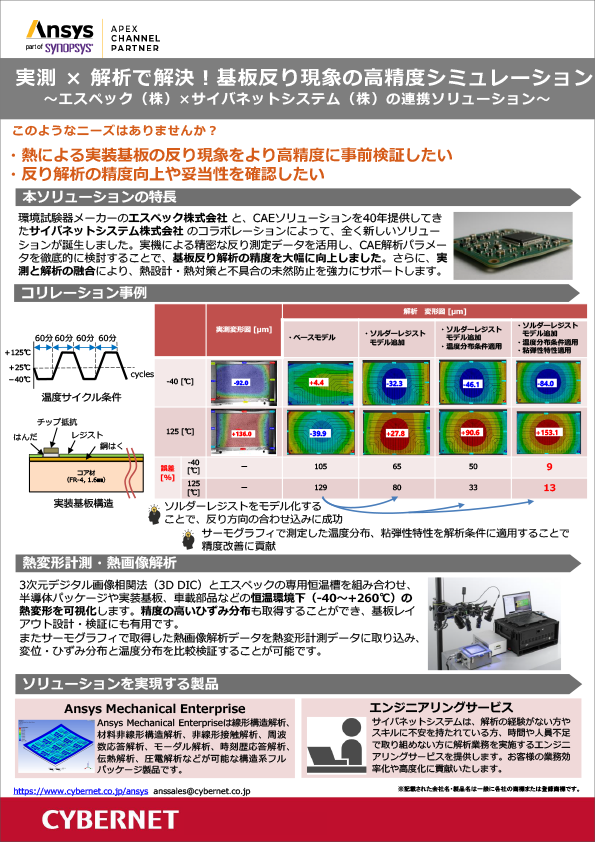

実測 × 解析で基板の熱変形問題を解決!基板反り現象の高精度シミュレーション

~エスペック(株)×サイバネットシステム(株)の連携ソリューション~

-

【全記事】CAEのあるものづくり vol.42

ユーザー様インタビュー記事7件を1冊に集約した保存版

-

誤差との上手なつきあい方 ~流体解析の計算誤差~ (完全保存版)

誤差との上手なつきあい方 前編・後編 を1冊にまとめた保存版 PDF

-

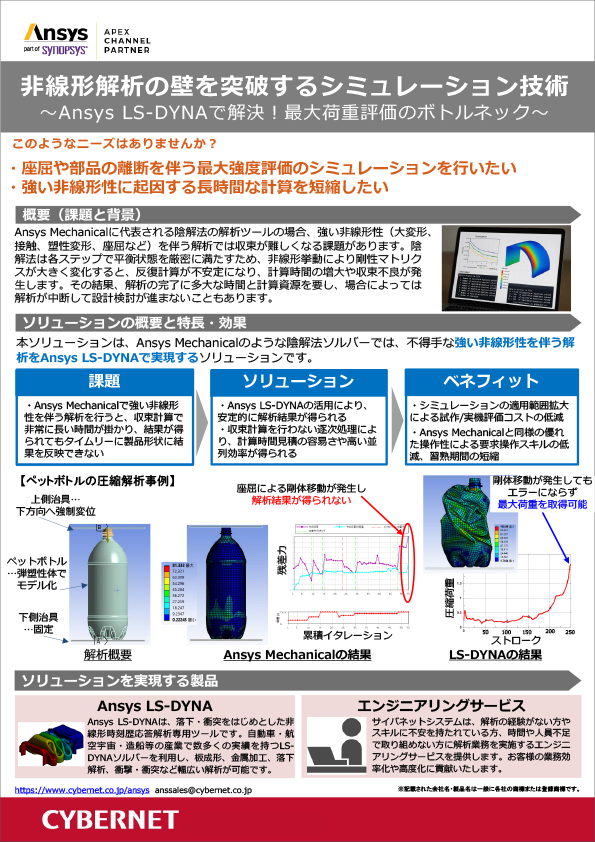

非線形解析の最大強度評価はAnsys LS-DYNAで解決!

~Ansys LS-DYNAで解決!最大荷重評価のボトルネック~

-

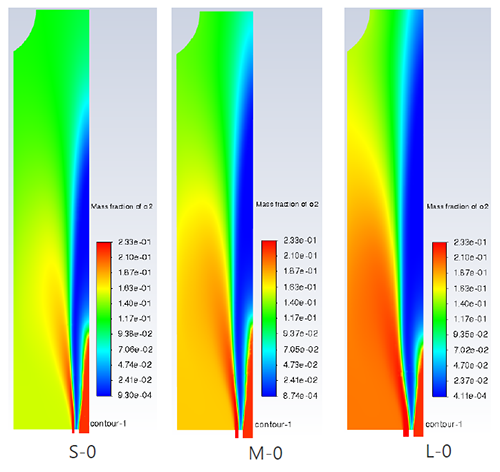

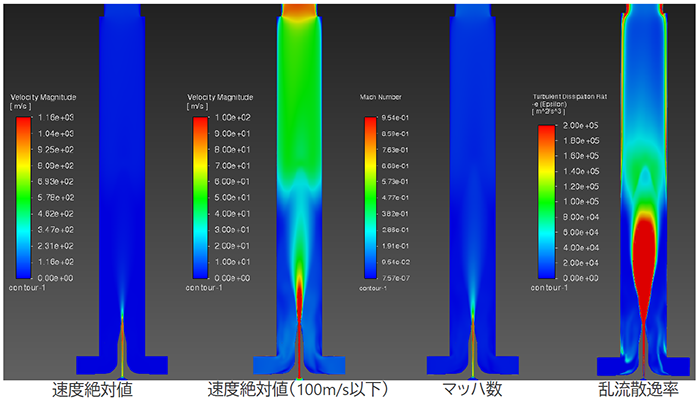

事例でご紹介!流体解析分野のエンジニアリングサービス ~解析業務の委託・立ち上げ支援・カスタマイズによる効率化など~

-

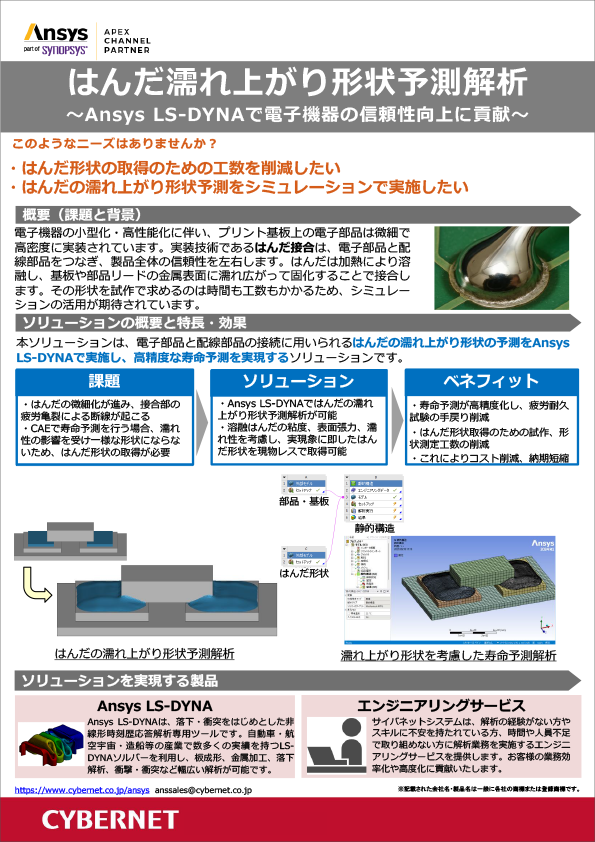

はんだ濡れ上がり形状予測解析で電子機器の信頼性向上

~Ansys LS-DYNAで電子機器の信頼性向上に貢献~

-

Ansys ユーザーのための PyAnsys 完全ガイド

Pythonで加速するCAEワークフロー

-

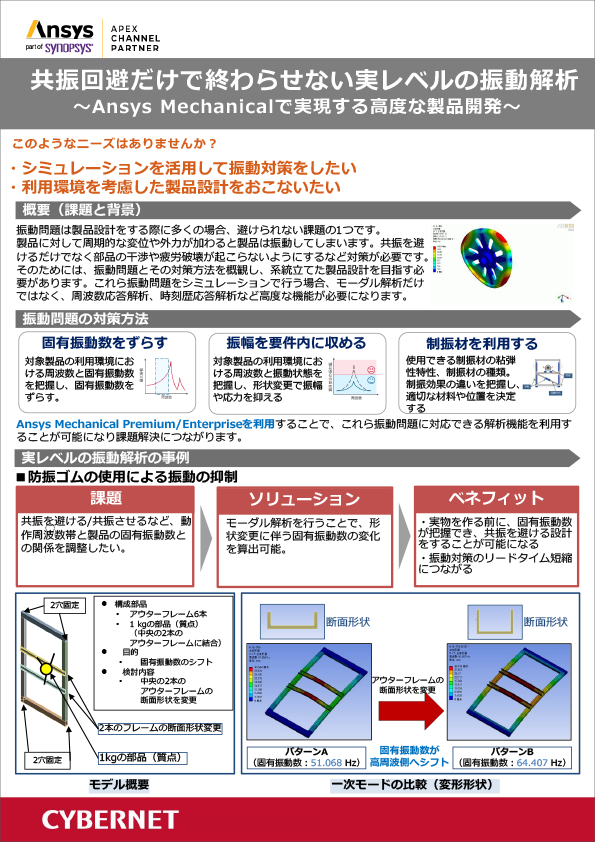

共振回避だけで終わらせない振動解析の進め方を解説(周波数応答・時刻歴まで)

~Ansys Mechanicalで実現する高度な製品開発~