セミナー・イベント

【Web配信】2.5D/3D-IC 実装技術への電磁界解析の適用

高精度な高速伝送特性評価を設計段階で実現!

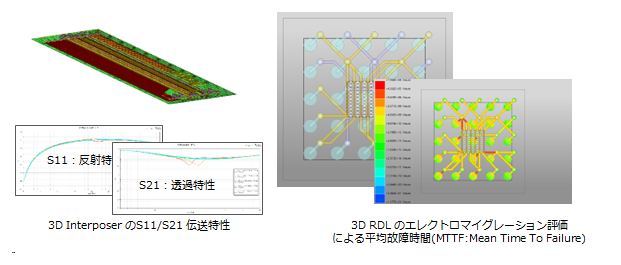

半導体製品の高速化、高機能化、低消費電力化には、シリコンウエハー上のパターンの微細化技術が必要となりますが、プロセスの複雑化と高コスト化により、微細化は限界と言われています。

この課題に対し、CPU や Memory など、異なるプロセスノードや機能を持つ複数の IC chip を同じ基板上に高密度で実装し、処理速度を向上させるパッケージング技術が注目されています。

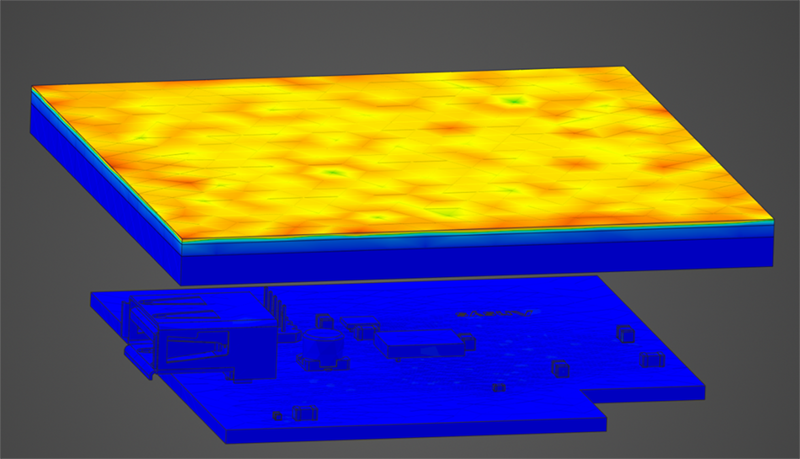

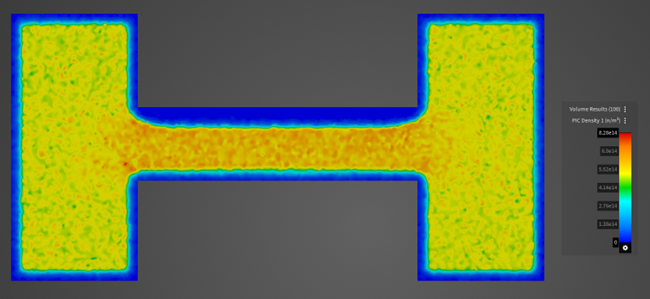

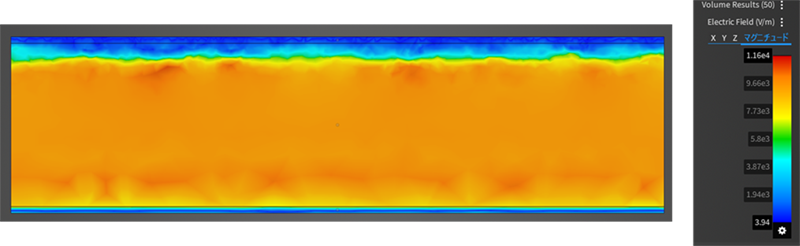

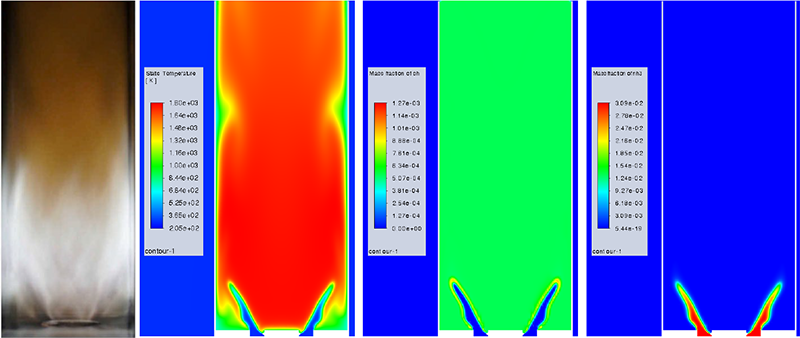

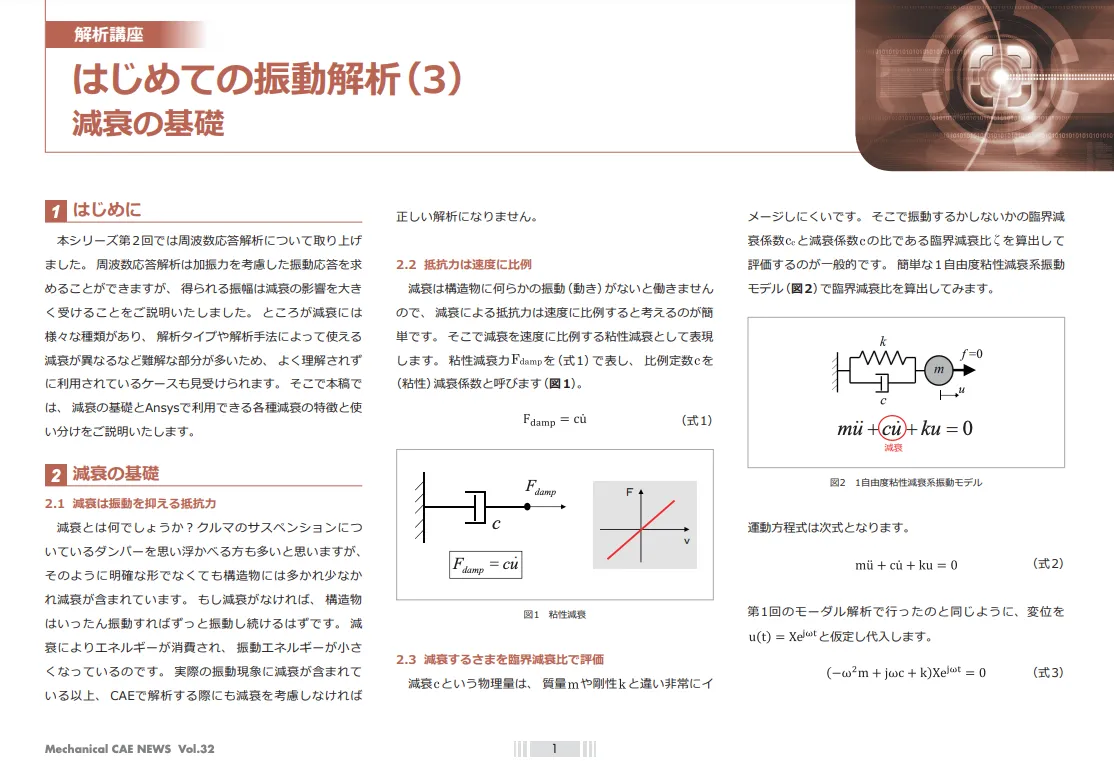

この技術で重要なのが、IC Chip の高密度 Fan-Out のための再配線層(RDL:Re-Distribution Layer) 、複数の IC Chip と基板を電気的に接続する際に中継部となる Interposer、さらに、IC Chip の Die を積層に積み上げ、Die 間を貫通することで接続する TSV(Through-silicon via)と呼ばれる電気接続ビアです。

しかし、これらの設計は容易なものではなく、IC Chip の高密度実装要求による微細 RDL のエレクトロマイグレーションへの信頼性対応要求、TSV や Interposer には IC の高機能化に伴う高いデータレートと高周波信号の伝送要求、これら要素を短期間かつ効率的に設計し、目標のパフォーマンスを実現することが要求されます。

本ウェビナーでは、 2.5D/3D-IC 化実装技術に対して電磁界解析を適用した性能評価の適用例についてご紹介します。

- 種類

- Ansysウェビナー

- 受講料

- 無料

- 対象者

- どなたでもご参加いただけます

日程・お申し込み

※終了時刻は多少前後する場合がございます。

開催概要

|

開催会場 |

本イベントはZoomを用いたWebセミナー形式での開催となります。 |

|---|---|

|

定員数 |

150名 |

|

対象 |

・半導体パッケージの開発に従事している方 |

|

製品 |

Ansys HFSS |

|

解析分野 |

電磁界解析全般 |

|

参加費 |

無料 (事前登録制) |

|

主催 |

サイバネットシステム株式会社 |

アジェンダ

1.2.5D/3D-IC化の背景

2.実装技術の課題

3.解析例の紹介

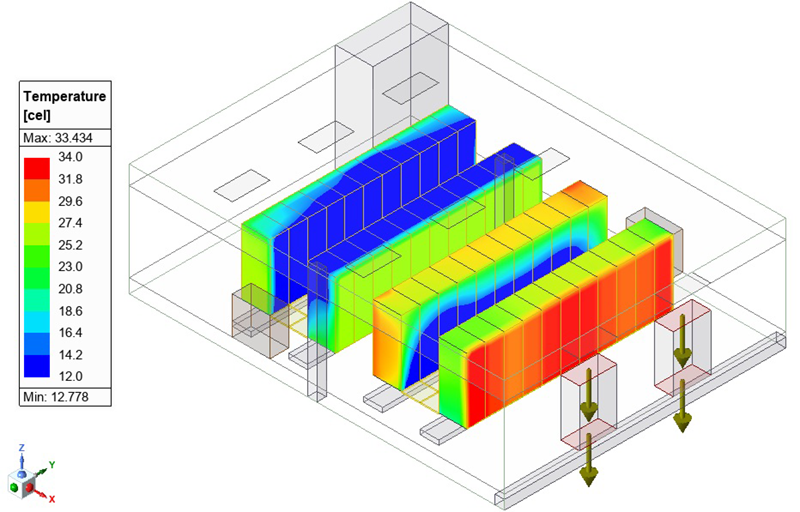

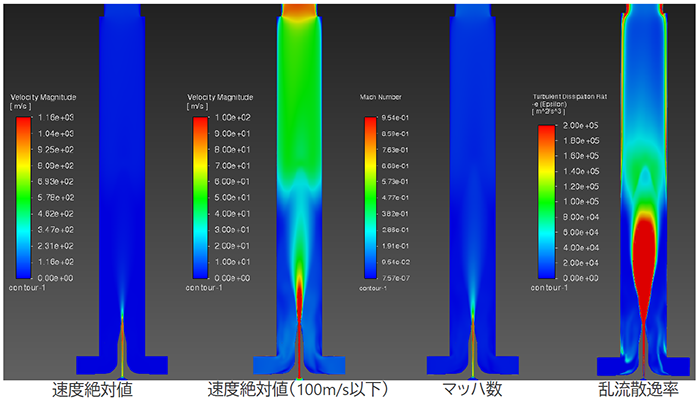

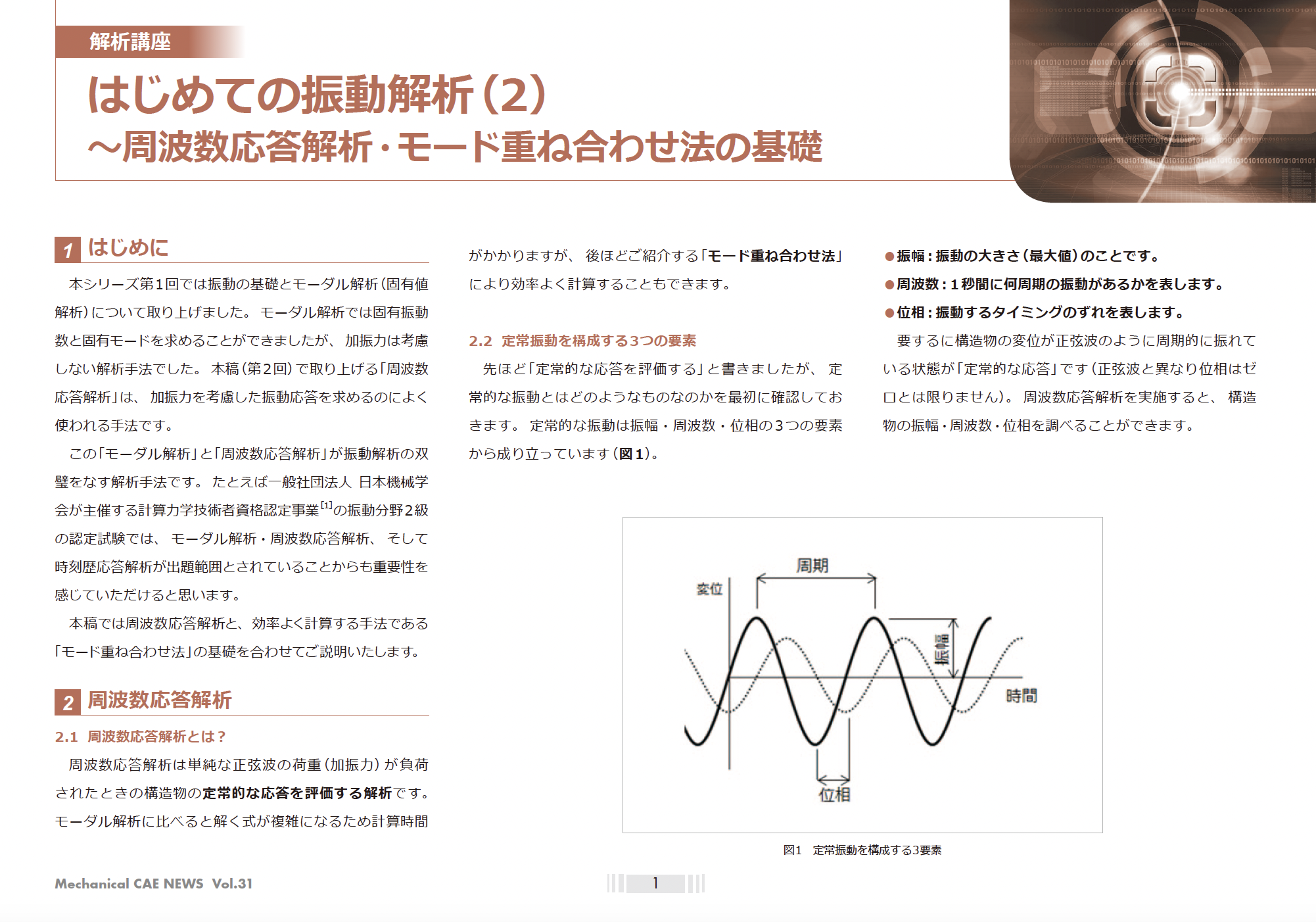

- Interposer の高速伝送特性の解析

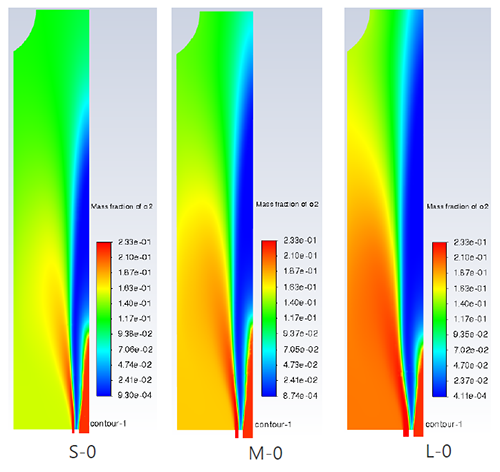

- TSV の高速伝送特性の解析

- RDL のエレクトロマイグレーション解析によるMTTF評価