解析事例

電源ノイズ波形の解析結果を考慮したEMI解析

こんな方におすすめ

- PCB上のデカップリングキャパシタと放射ノイズ特性の相関関係を検証したい回路・PCB設計者

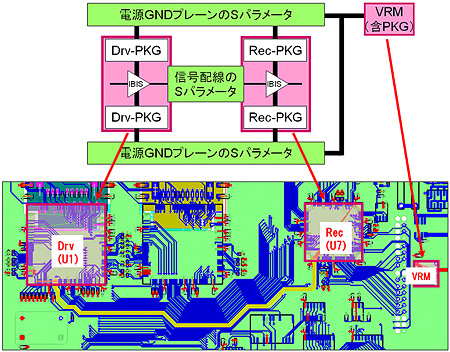

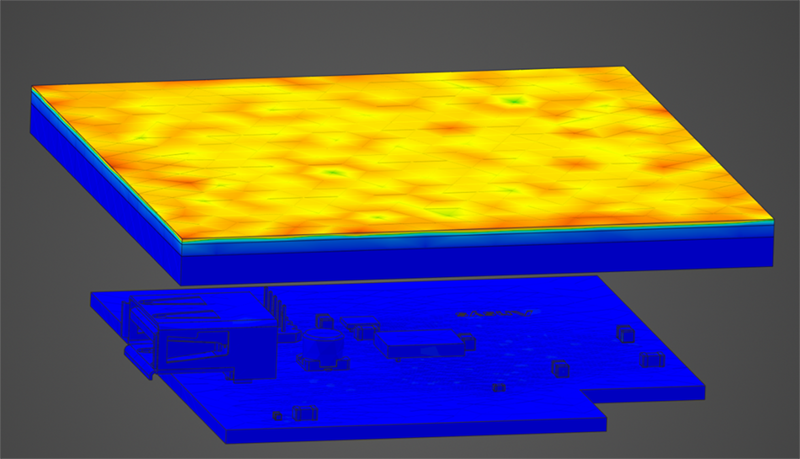

- 図1は電源ノイズ解析結果を考慮したEMI解析のブロック図とPCB実装図との対応図です。

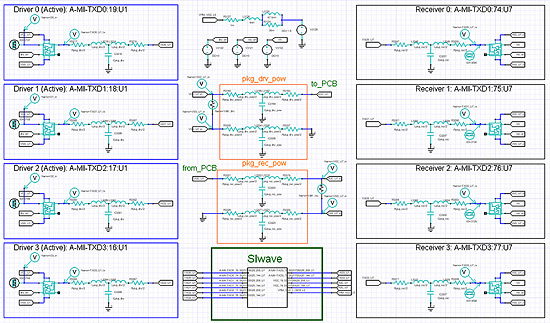

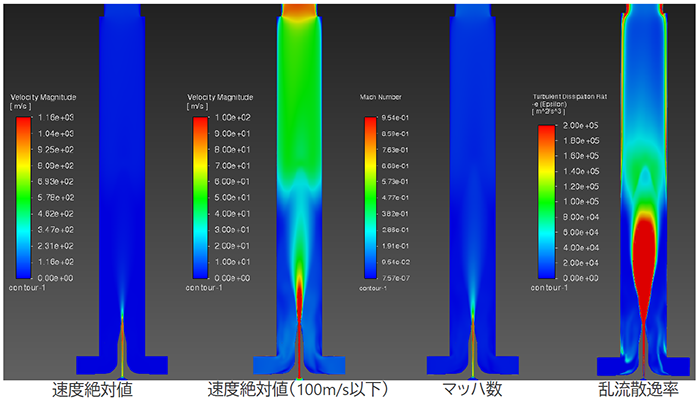

- 図2はDesigner のシミュレーション回路図です。PCBのSパラメータはSIaveで解析して求めます。

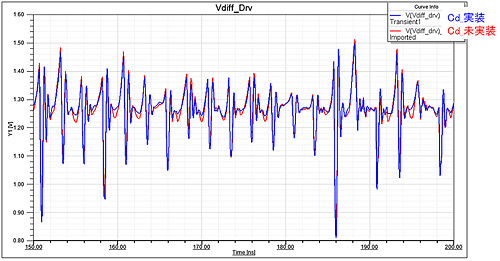

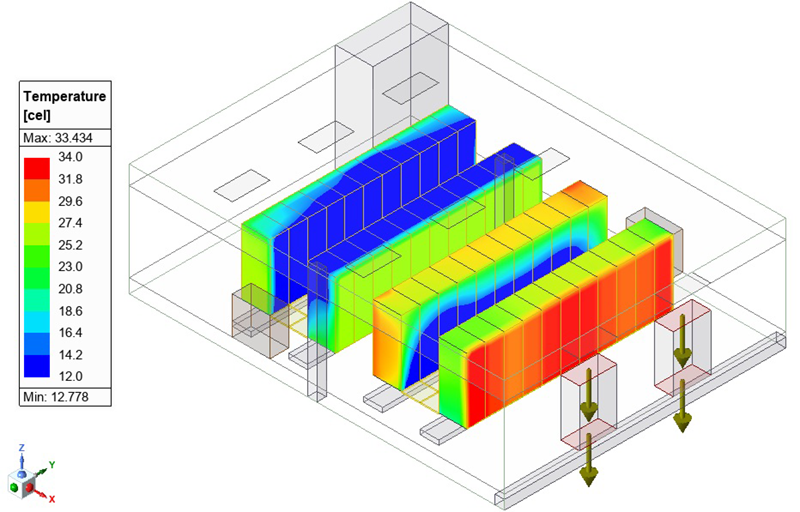

- 図3はドライバのデカップリングキャパシタを未実装した場合(赤色)と実装した場合(青色)について、電源ノイズ V(Vdiff_drv) 波形を求めた結果です。

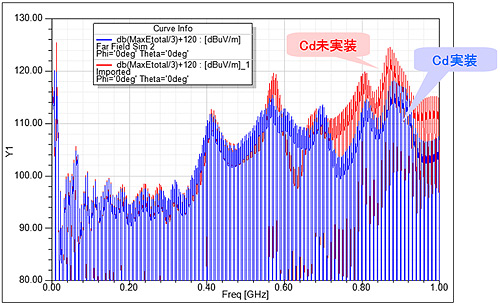

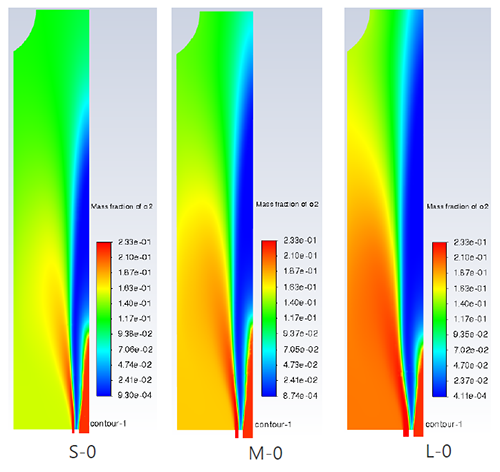

- 図4はドライバICのデカップリングキャパシタ(Cd)を実装/未実装時における遠方界(3m)をシミュレーションで求めて比較表示したものです。この図からはCdの実装によりEMIノイズが抑えられているのが確認できます。

解析モデル

図1 電源ノイズ解析結果を考慮したEMI解析のブロック図とPCB実装図との対応図

図2 Designer のシミュレーション回路図

解析結果

図3 ドライバのデカップリングキャパシタを未実装した場合(赤色)と実装した場合(青色)の電源ノイズ V(Vdiff_drv) 波形

図4 ドライバのデカップリングキャパシタを未実装した場合(赤色)と実装した場合(青色)の遠方界(3m)解析結果比較

関連キーワード

関連情報

関連する解析事例

MORE関連する資料ダウンロード

MORE-

CAE投資のROI可視化でシミュレーションの利用価値を高める

-

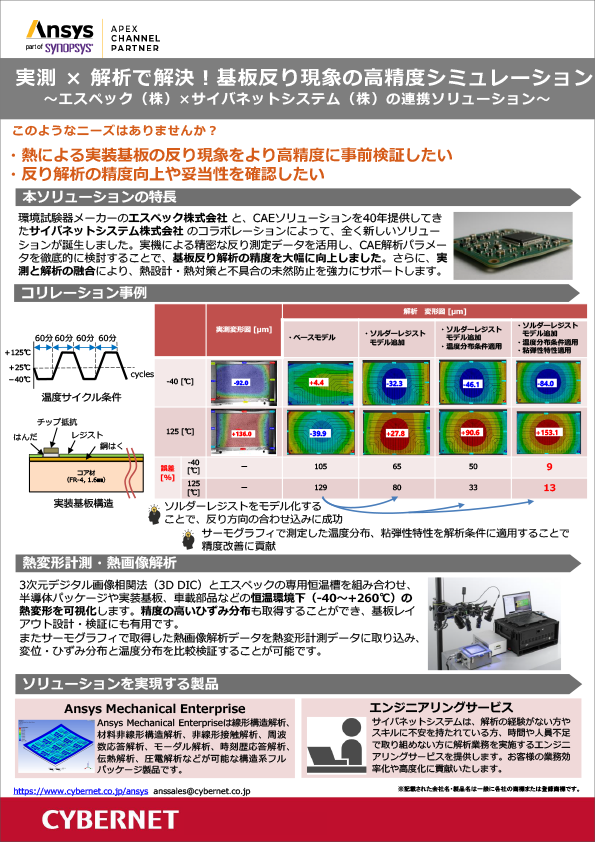

実測 × 解析で基板の熱変形問題を解決!基板反り現象の高精度シミュレーション

~エスペック(株)×サイバネットシステム(株)の連携ソリューション~

-

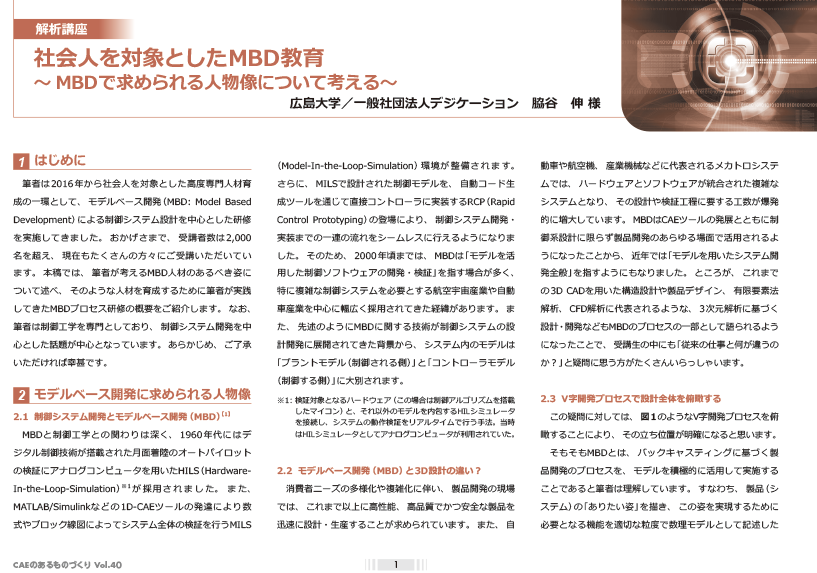

【全記事】CAEのあるものづくり vol.42

ユーザー様インタビュー記事7件を1冊に集約した保存版

-

誤差との上手なつきあい方 ~流体解析の計算誤差~ (完全保存版)

誤差との上手なつきあい方 前編・後編 を1冊にまとめた保存版 PDF

-

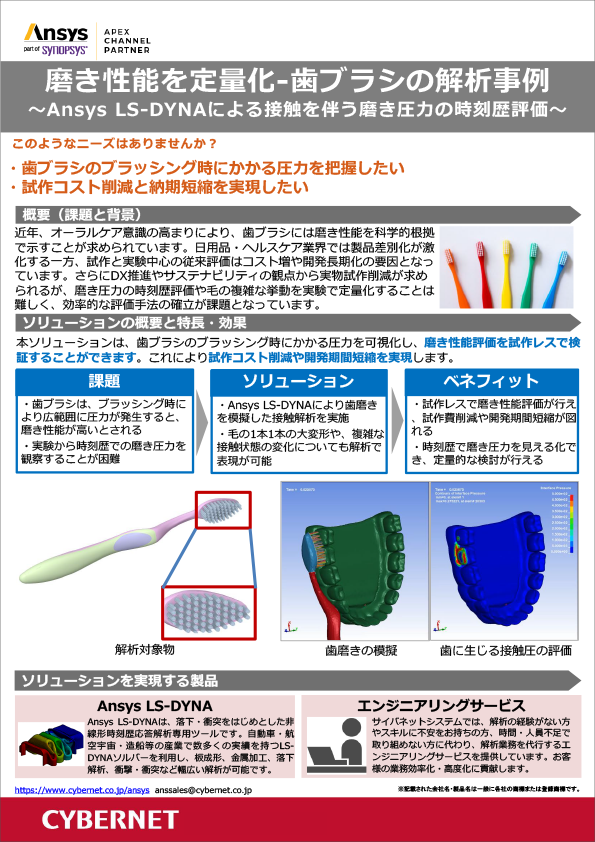

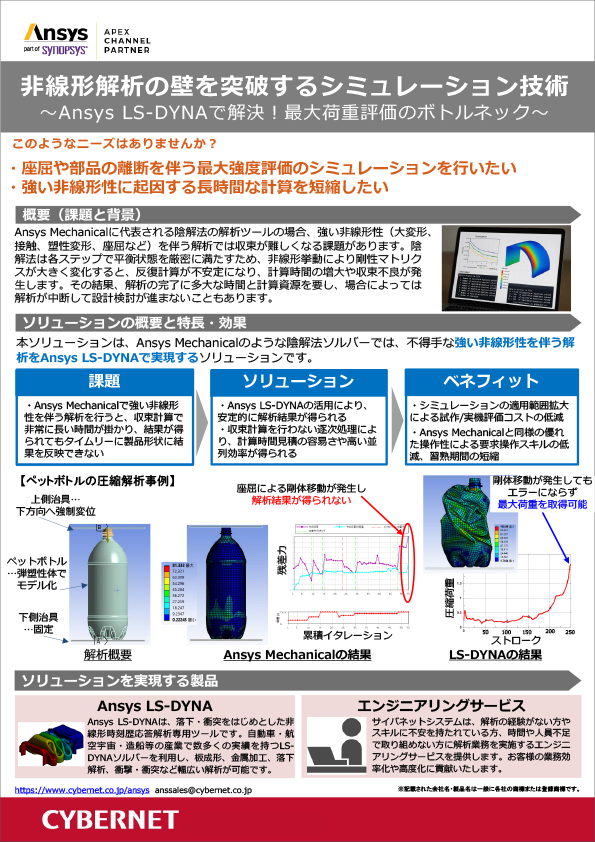

非線形解析の最大強度評価はAnsys LS-DYNAで解決!

~Ansys LS-DYNAで解決!最大荷重評価のボトルネック~

-

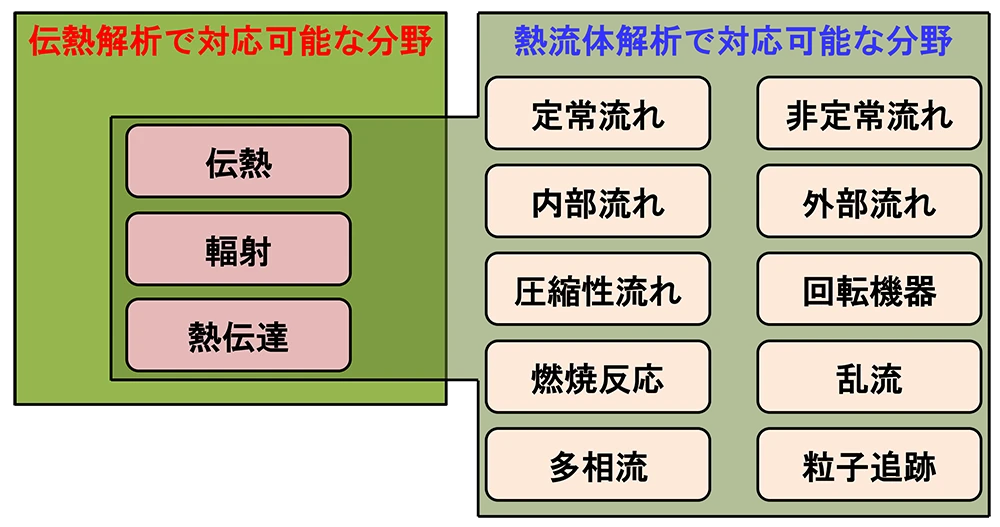

事例でご紹介!流体解析分野のエンジニアリングサービス ~解析業務の委託・立ち上げ支援・カスタマイズによる効率化など~

-

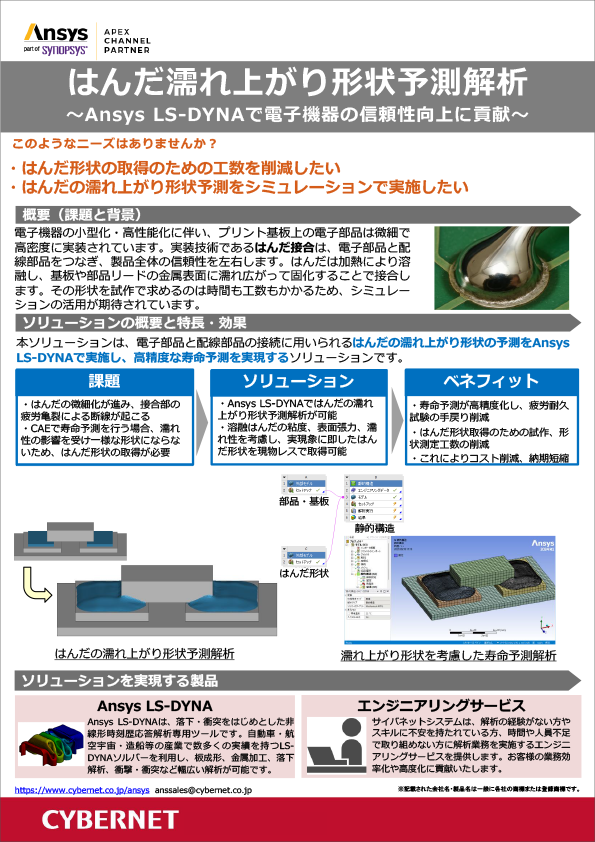

はんだ濡れ上がり形状予測解析で電子機器の信頼性向上

~Ansys LS-DYNAで電子機器の信頼性向上に貢献~

-

Ansys ユーザーのための PyAnsys 完全ガイド

Pythonで加速するCAEワークフロー