解析事例

JEDEC規格に準拠したDDR3メモリのSI解析事例

こんな方におすすめ

- 目標とする配線スキューを満足した基板レイアウトができているか確認したい。

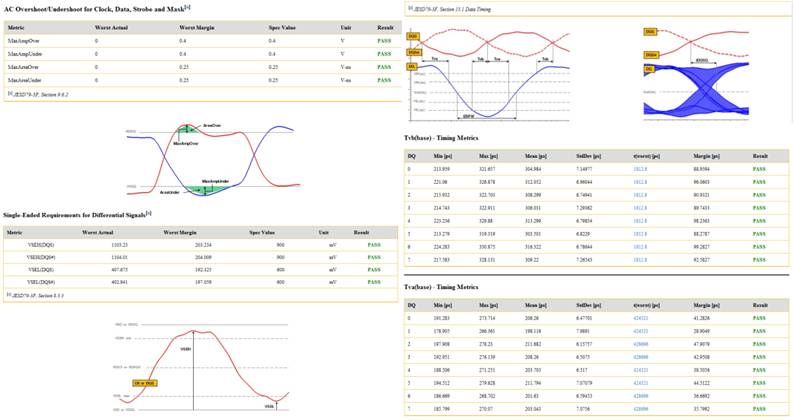

- JEDEC規格に対する波形、タイミングマージンを確認したい。

- デバイスの駆動設定や受動部品(ダンピング抵抗など)の定数を最適化したい。

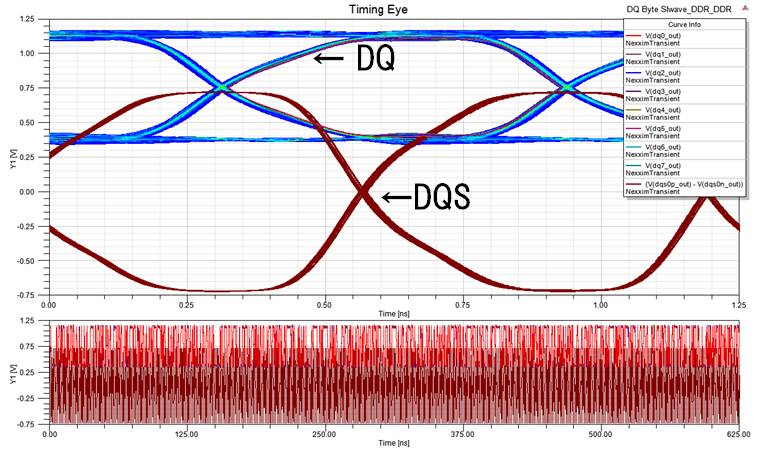

メモリの転送速度が高速化し、基板配線に許容されるスキューがますます厳しくなっています。基板レイアウトの電磁界解析と回路シミュレータの連携により、コントローラICとDDR3メモリ間の波形、タイミング解析を実施します。その結果から、JEDEC規格に対する合否判定と、マージンをレポート機能により自動算出します。

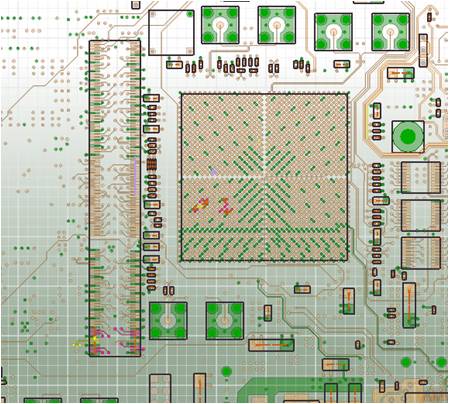

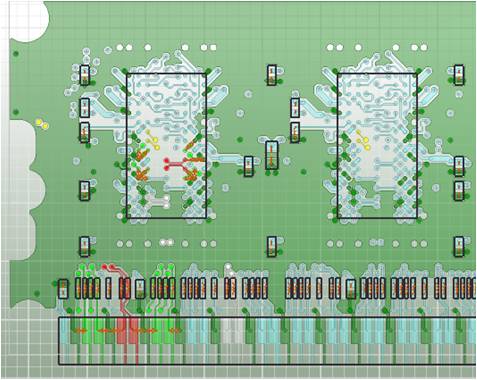

解析モデル

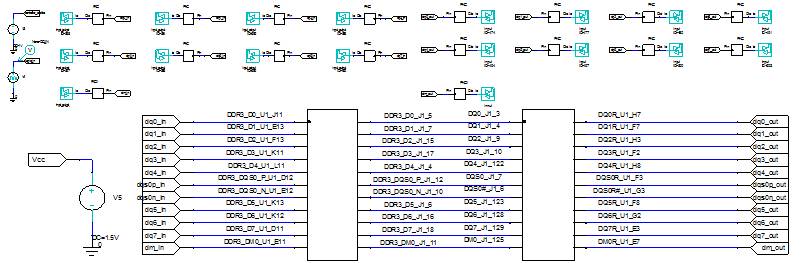

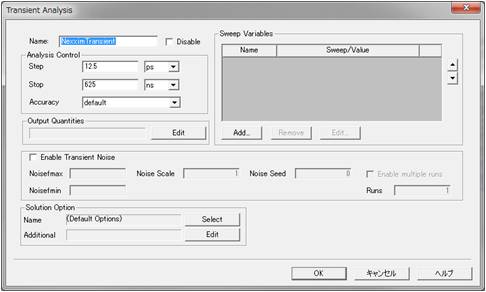

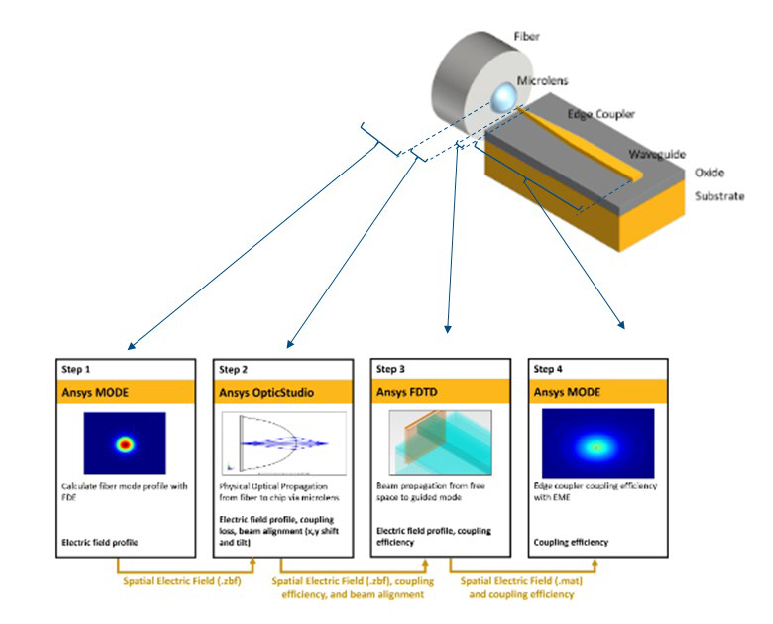

解析フロー

解析結果

対応プロダクト

以下のライセンスを使用

関連キーワード

関連情報

関連する解析事例

MORE関連する資料ダウンロード

MORE-

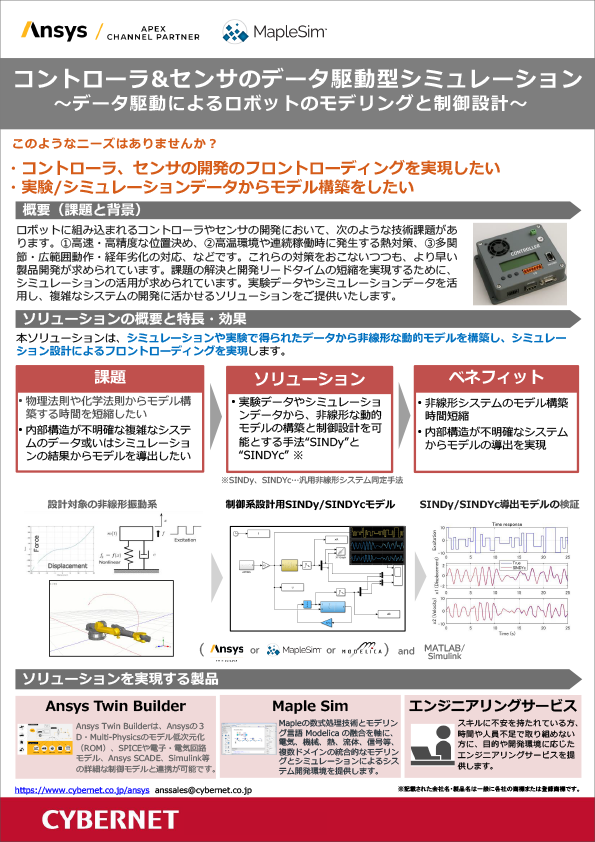

コントローラ&センサのデータ駆動型シミュレーション

~データ駆動によるロボットのモデリングと制御設計~

-

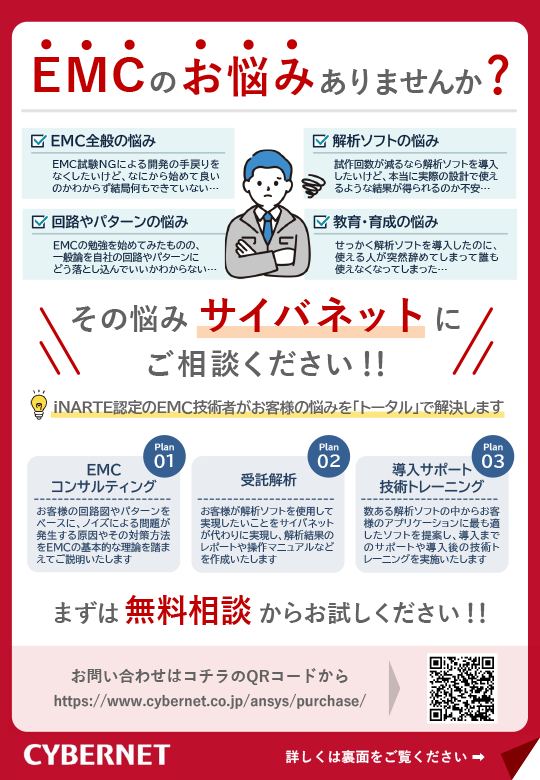

EMCのお悩みありませんか? ~EMCソリューション~

-

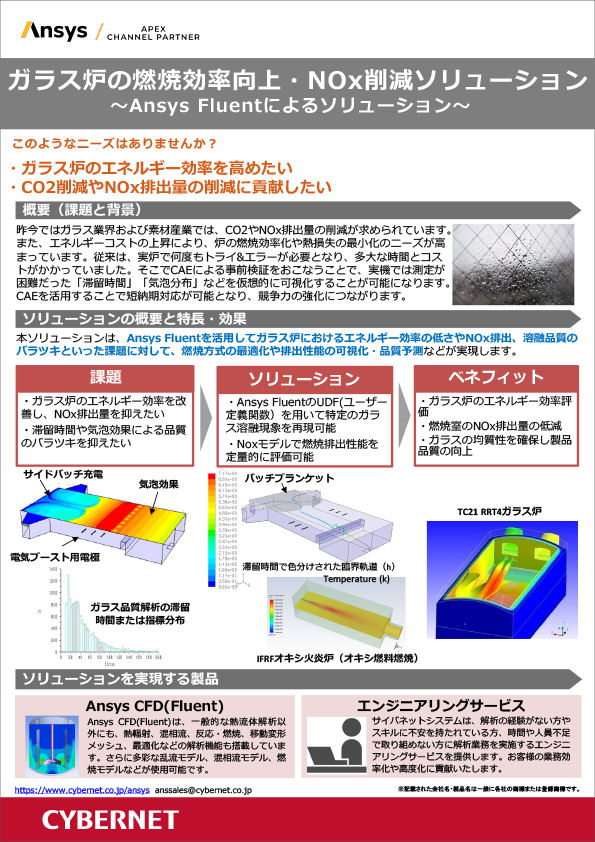

ガラス炉の燃焼効率向上・NOx削減ソリューション ~Ansys Fluentによるソリューション~

~Ansys Fluentによるソリューション~

-

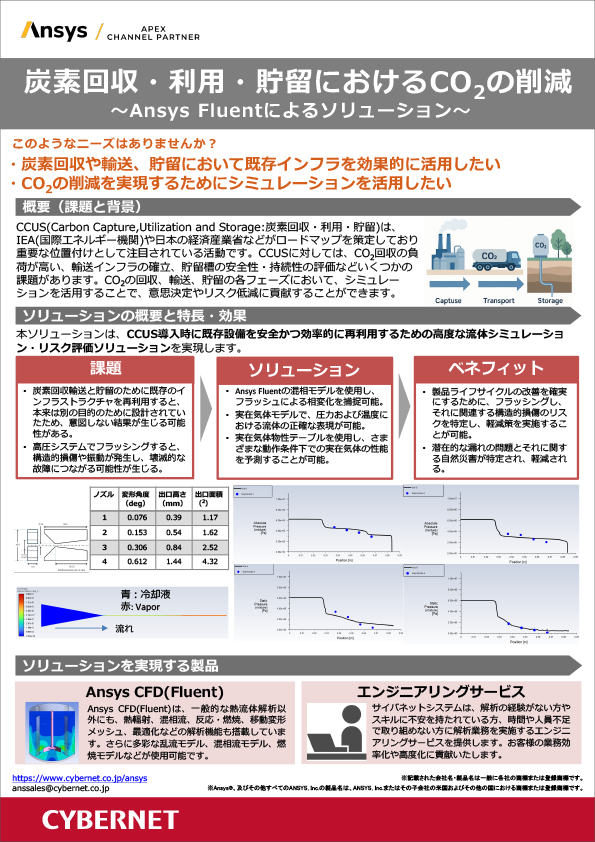

炭素回収・利用・貯留におけるCO2の削減 ~Ansys Fluentによるソリューション~

~Ansys Fluentによるソリューション~

-

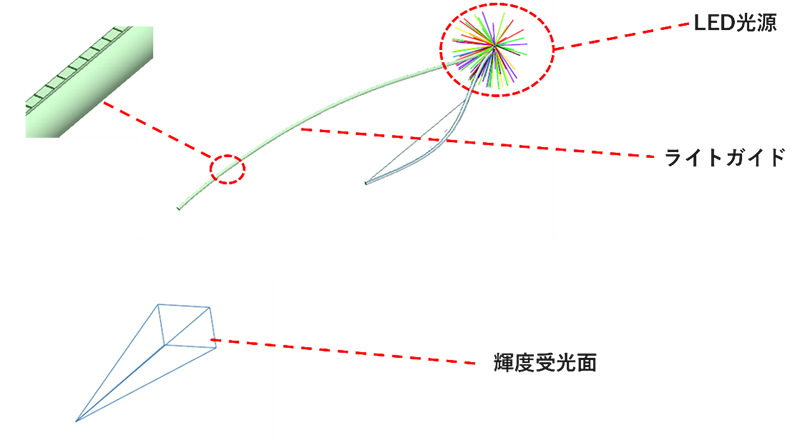

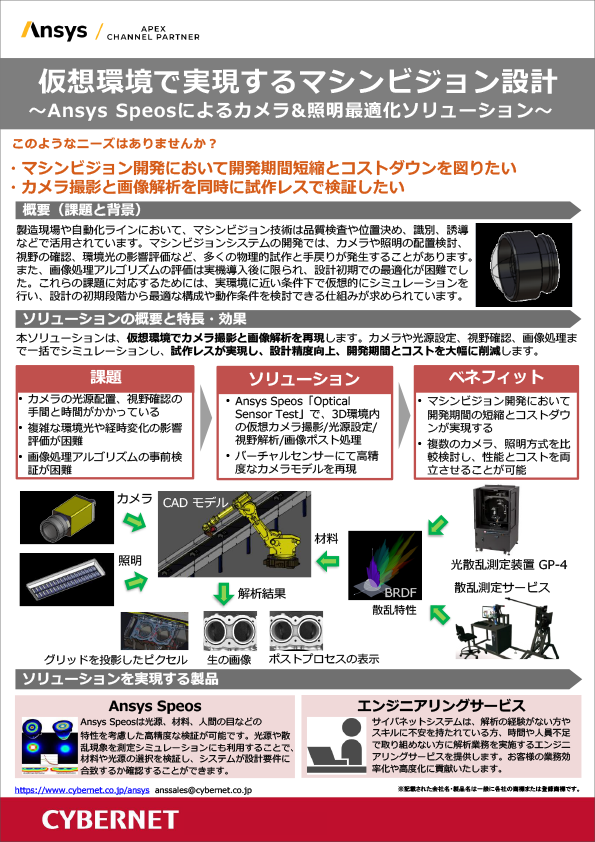

仮想環境で実現するマシンビジョン設計~Ansys Speosによるカメラ&照明最適化ソリューション~

~Ansys Speosによるカメラ&照明最適化ソリューション~

-

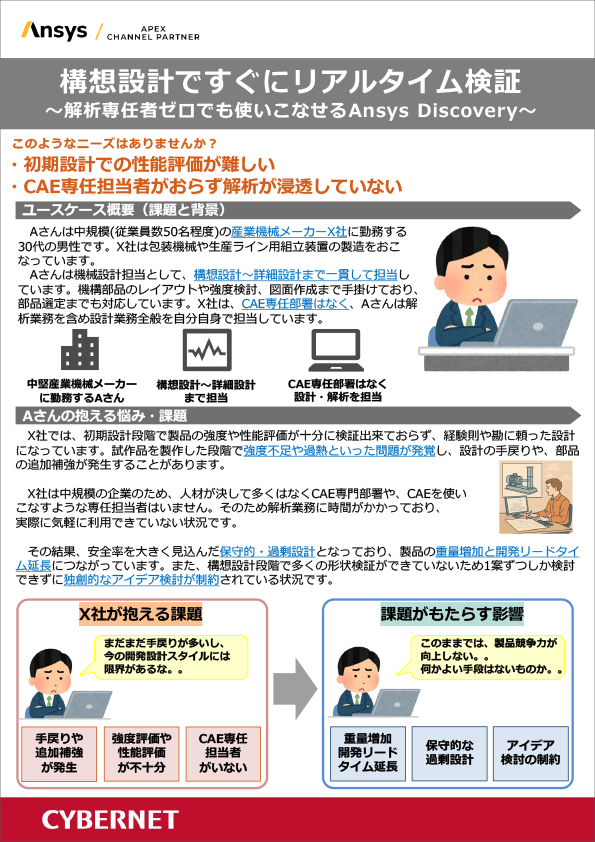

構想設計ですぐにリアルタイム検証 ~解析専任者ゼロでも使いこなせるAnsys Discovery~

~解析専任者ゼロでも使いこなせるAnsys Discovery~

-

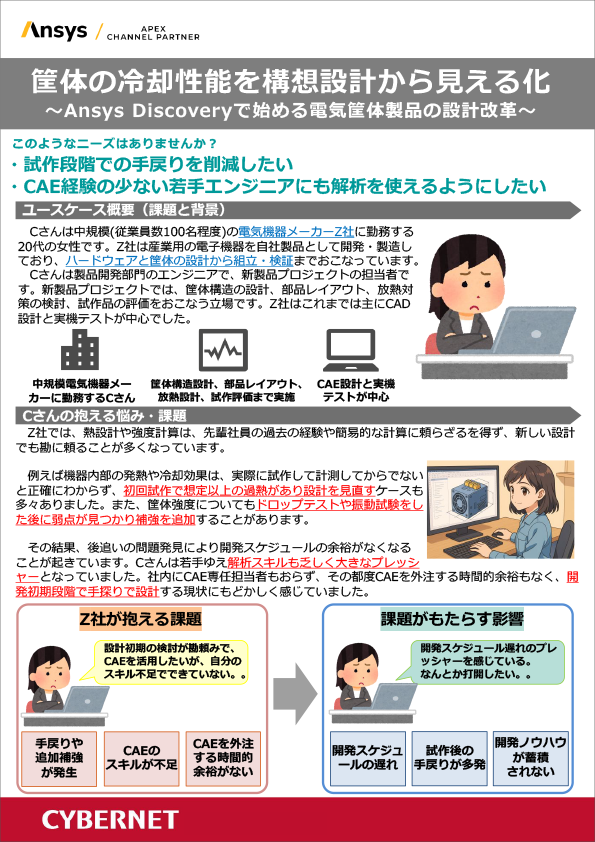

筐体の冷却性能を構想設計から見える化 (手戻りを削減できる)

~Ansys Discoveryで始める電気筐体製品の設計改革~

-

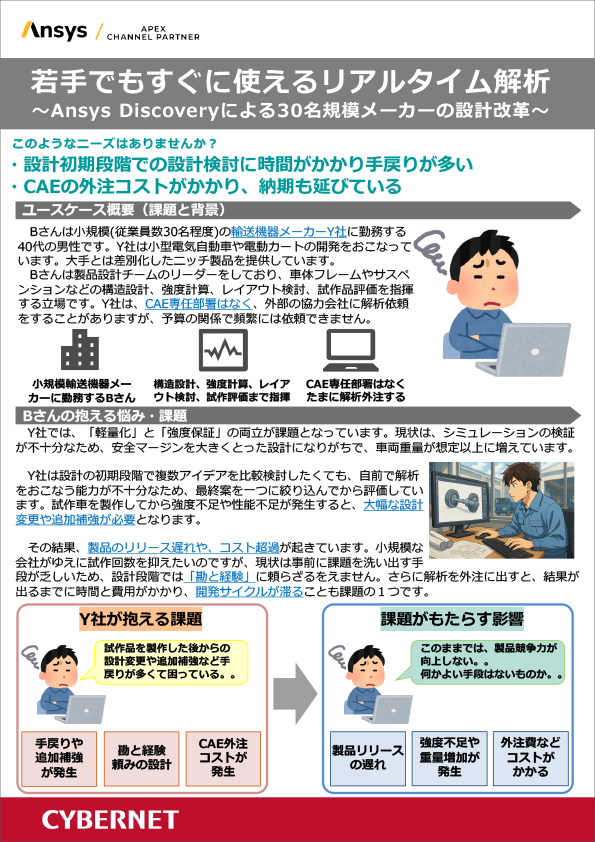

若手でもすぐに使えるリアルタイム解析 (勘と経験からの脱却)

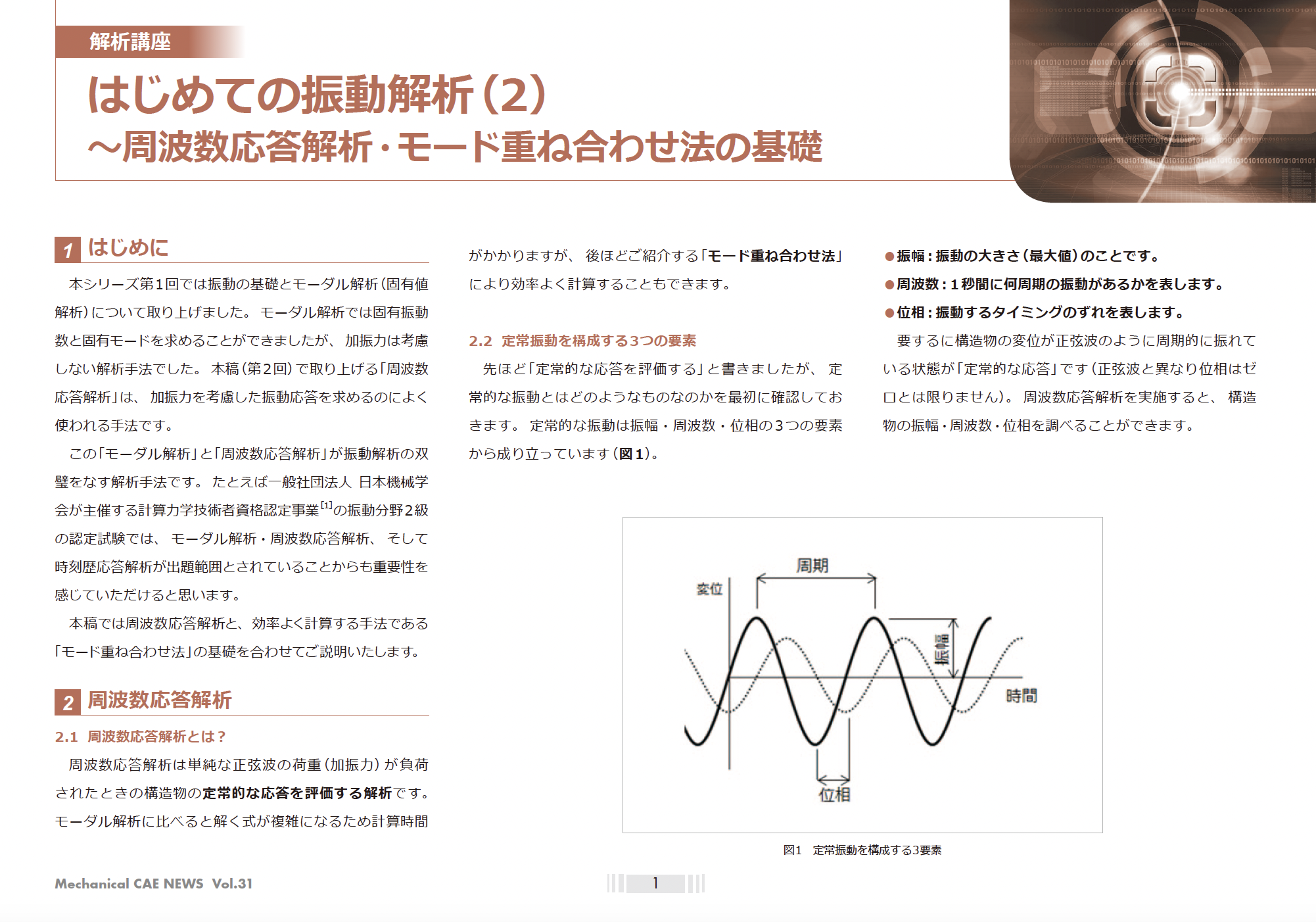

~Ansys Discoveryによる30名規模メーカーの設計改革~