解析事例

プリント基板と筐体のグランド接続時のESDノイズ解析

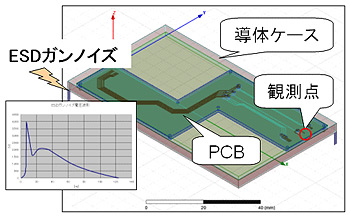

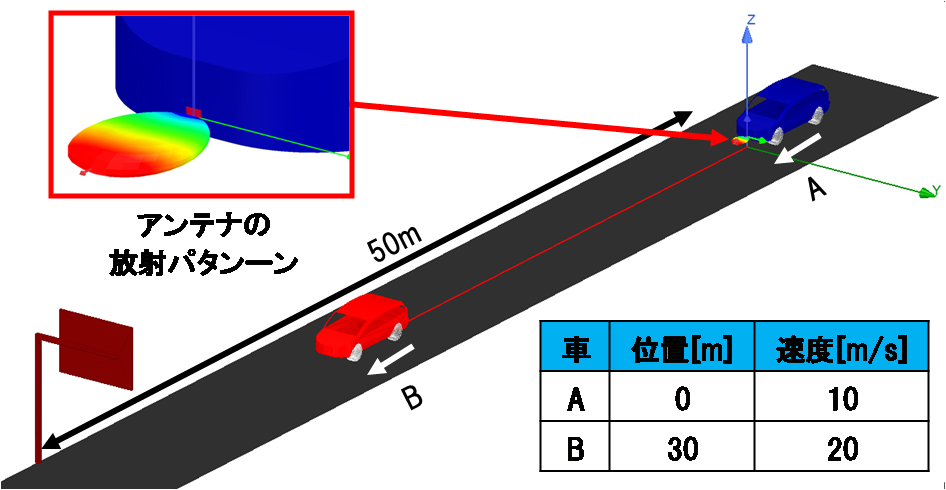

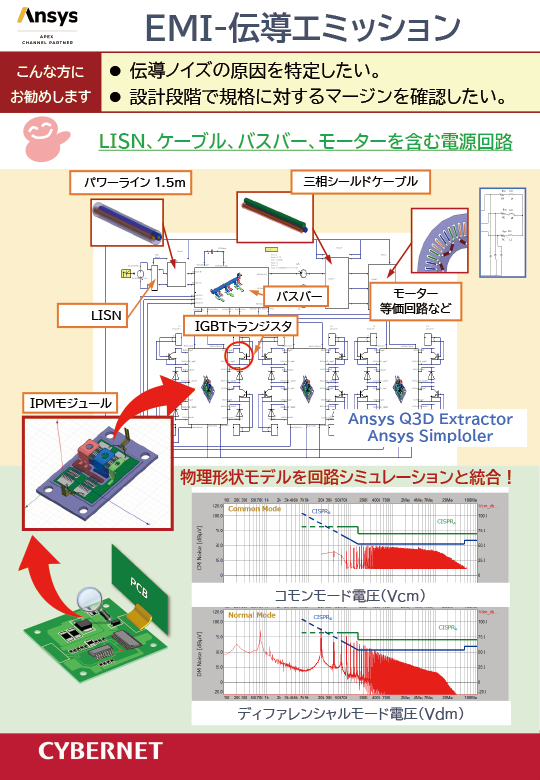

この事例はPCBの外側にある導体ケースの右上部に ESDガンノイズを印加したときの、各部の電界強度分布をシミュレーションし、各信号線のポートに発生するノイズ波形解析結果を紹介致します。

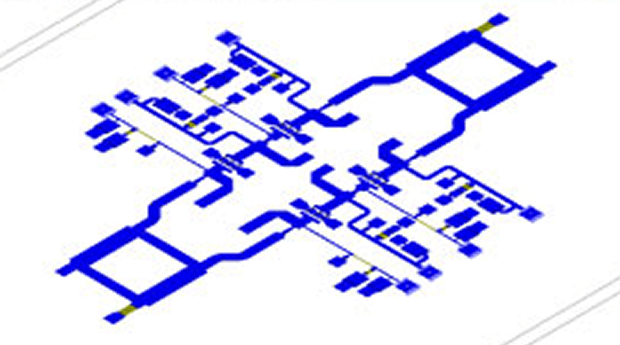

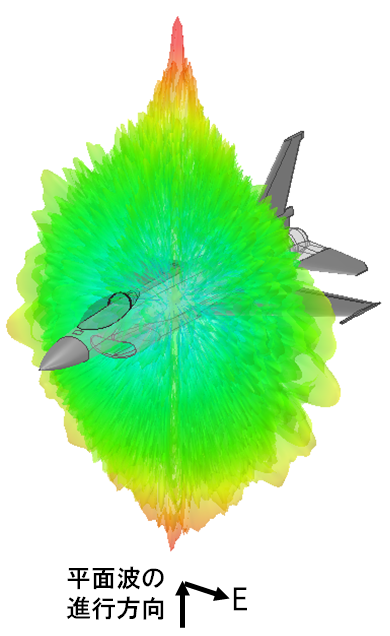

・ 図1は、 Ansys HFSS で作成したESDガンノイズ解析モデルの概観図です。導体ケースにピーク値4kVのノイズパルスを印加します。赤丸の場所はノイズ波形解析時の観測点です。

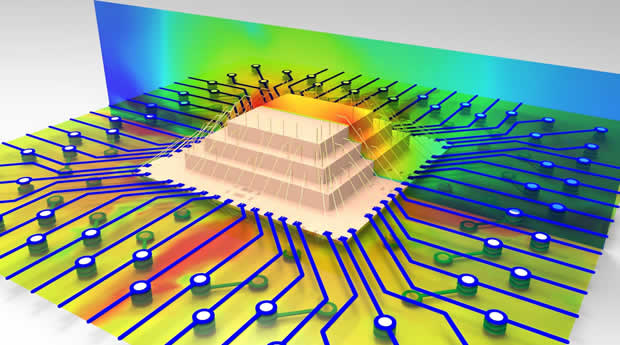

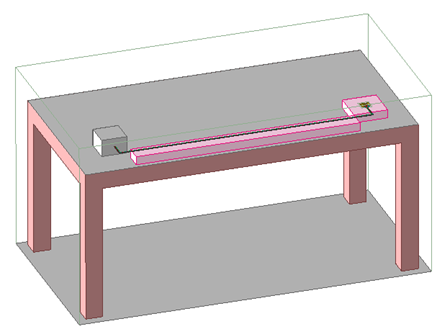

・ 図2は、Transient Solver を用いた解析結果です。ケースおよびPCBの表面電界強度の時間変化が確認できます。ケースの角の部分の電界強度が高くなっているのが確認できます。

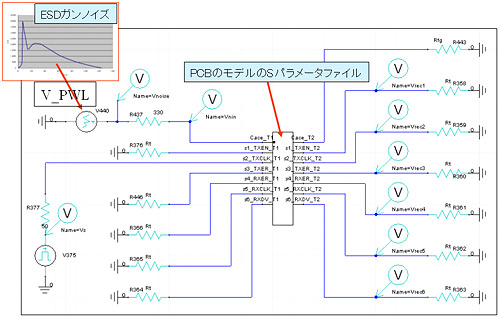

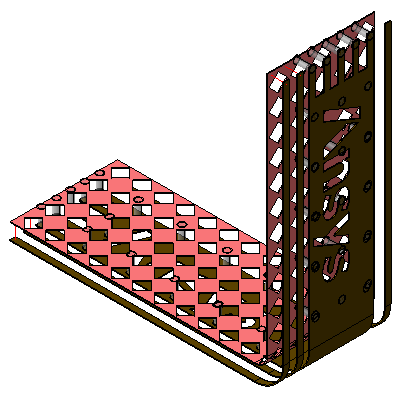

・ 図3は、Ansys HFSSで抽出したSパラメータファイルを用い、 Ansys Circuit (Ansys Designer) で波形解析を行うための回路図です。ここでは、ノイズ波形をPWL形式 で記述したテキストファイルを読み込んでシミュレーションしています。

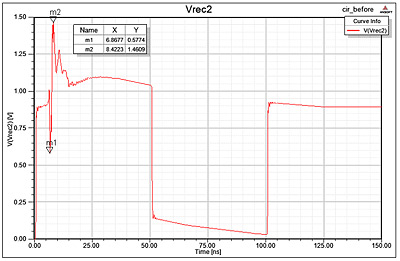

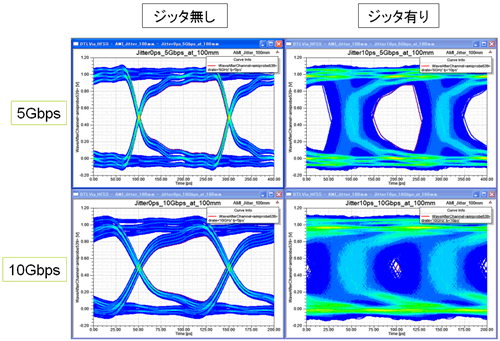

・ 図4はノイズ印加時に発生した観測点の電圧波形を示したものです。

解析モデル

図1 ESDガンノイズ解析モデル

解析結果

図2 電界強度の時間変化の様子

対応プロダクト

以下のライセンスを使用

Ansys HFSS+SI Option