Ansys HFSS

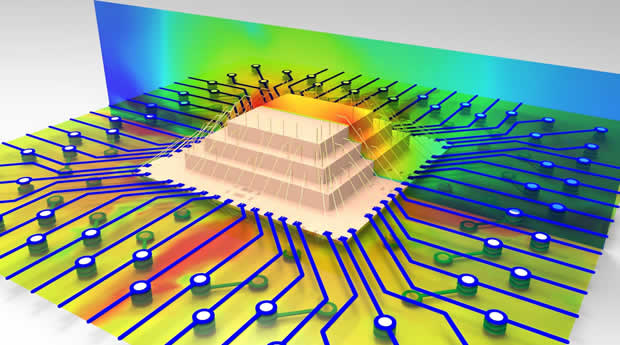

高周波3次元電磁界解析ソフトウェア

セミナー・イベント

※終了時刻は多少前後する場合がございます。

|

開催会場 |

本イベントはZoomを用いたWebセミナー形式での開催となります。 |

|---|---|

|

定員数 |

150名 |

|

対象 |

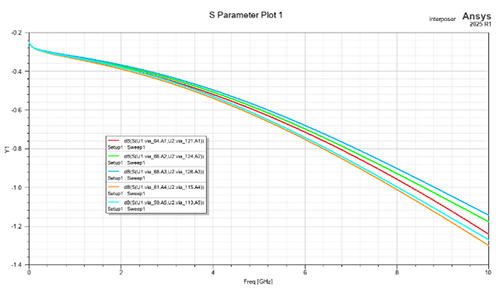

・半導体パッケージの開発に従事している方

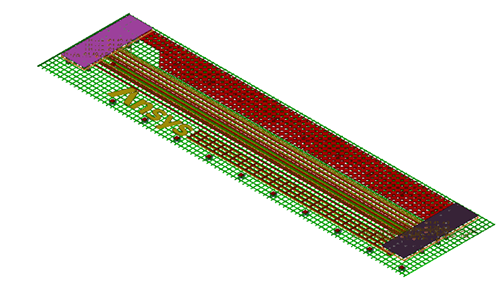

・半導体インターポーザの設計に従事している方

・半導体パッケージを含むPCBシステムの特性評価に従事している方

|

|

製品 |

Ansys HFSS |

|

解析分野 |

電磁界解析全般 |

|

参加費 |

無料 (事前登録制) |

|

主催 |

サイバネットシステム株式会社 |

Ansys、ならびにANSYS, Inc. のすべてのブランド名、製品名、サービス名、機能名、ロゴ、標語は、米国およびその他の国におけるANSYS, Inc. またはその子会社の商標または登録商標です。その他すべてのブランド名、製品名、サービス名、機能名、または商標は、それぞれの所有者に帰属します。本ウェブサイトに記載されているシステム名、製品名等には、必ずしも商標表示((R)、TM)を付記していません。 CFX is a trademark of Sony Corporation in Japan. ICEM CFD is a trademark used by Ansys under license. LS-DYNA is a registered trademark of Livermore Software Technology Corporation. nCode is a trademark of HBM nCode.