事例紹介

リセットラインの電圧変動を抑制するESD対策の検証

解析分野 : 電磁界解析 業界:自動車・エレクトロニクス

解析概要

DEMITASNXによるESDルールチェックで検出されたエラーを対象に、Ansys SIwaveを用いて電磁界解析を実施しました。リセットラインに対して、保護キャパシタの追加およびグランドシールドパターンの追加といった対策を行い、対策前後の電圧変動を比較することで、ESD対策の有効性を検証しています。

- プレーン貫通エラー

- リセットライン保護エラー

こんな方におすすめ

- リセットラインなどの制御信号におけるESD対策に課題を感じている方

- 保護部品の配置やグランド設計の妥当性を定量的に評価したい方

- シミュレーションを活用したESD対策を検討しているが、解析対象の選定に悩んでいる方

背景/課題

プリント基板設計におけるESD(静電気放電)対策では、外部から印加される過渡的な電流や電圧が回路に与える影響を適切に抑制することが重要です。特にリセットラインなどの制御信号は、ノイズの影響を受けやすく、わずかな電圧変動でも誤動作を引き起こす可能性があります。

しかし、ESDの影響は瞬間的かつ広範囲に伝搬するため、基板全体の構造やグランド・電源プレーンの状態、配線経路など複数の要因が複雑に絡み合い、設計段階でそのリスクを正確に把握することは容易ではありません。さらに、保護部品の配置やグランド経路の設計が不適切な場合、電流の逃げ道が確保されず、特定の信号ラインに過大な電圧変動が発生することがあります。

さらに、シミュレーションによる評価は有効であるものの、解析対象の選定が難しく、すべてを網羅的に評価することは現実的ではありません。その結果、潜在的なESDリスクを十分に把握できないまま設計が進み、試験段階で問題が顕在化するという課題があります。

解析の仕様

解析モデル

サンプル基板データ

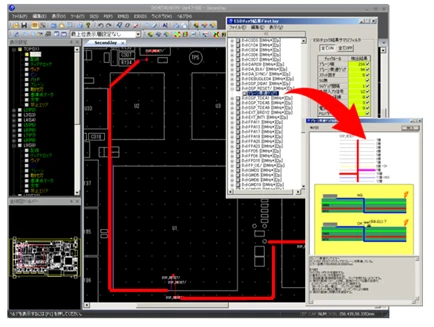

サンプル基板データを使用してESDルールチェックを実行します。そして、ESDルールチェックの結果より、リセットラインに関するエラーがありました。本事例では、2つのエラーを対象に解析を行っています。

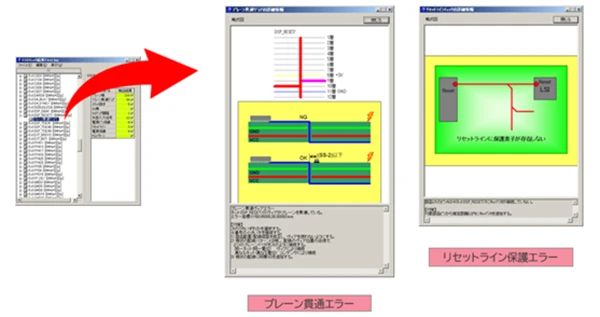

ESDルールチェックを実行した結果です。エラーは以下の2つです。

- プレーン貫通エラー(リターン経路の不連続)

- リセットライン保護エラー(保護部品のみ配置)

Ansys SIwaveによるSパラメーター解析と電圧変動解析

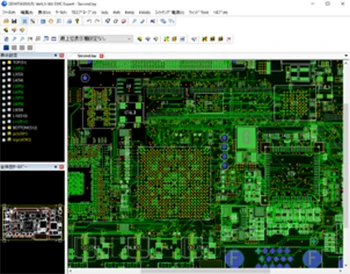

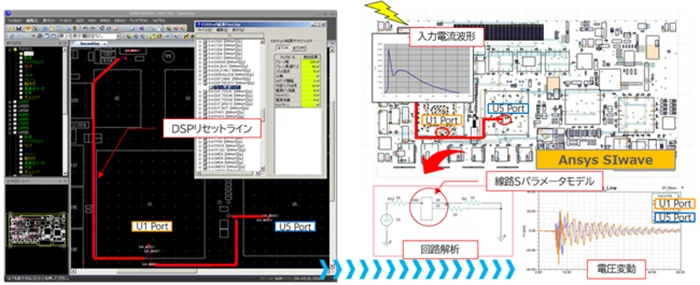

Ansys SIwaveで、ESDルールチェックエラーのありましたDSPリセットラインのノイズを確認します。対象PCBのグランドラインに、規格値の電流波形を入力して、リセットラインの電圧変化を評価しました。Ansys SIwaveで、PCB全体からリセットラインとグランドを含む線路のSパラメーターをモデル化し、等価回路図として電圧変動を計算します。

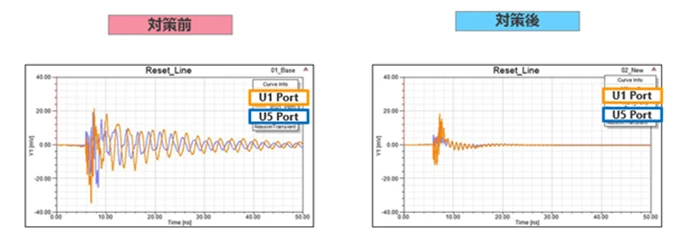

リセットライン 電圧変動解析結果

解析結果

DEMITASNXのESDルールチェックで検出されたエラー箇所に対して、アドバイスに基づく対策を適用しました。具体的には、リセットラインに保護キャパシタを追加し、プレーン貫通エラー対策としてグランドシールドパターンを追加しています。その結果、Ansys SIwaveによる解析において、対策前後でリセットラインの電圧変動に明確な差が確認されました。対策後は電圧変動が大幅に低減しており、ESD印加時のノイズ影響が抑制されていることが分かります。これにより、ルールチェックで指摘された問題とその対策が、実際の電気的挙動においても有効であることが確認されました。

リセットライン 対策

リセットライン 電圧変動解析結果

本解析の効果

今回、DEMITASNXによるESDルールチェックでリセットラインの保護不足やプレーン貫通といった問題箇所を抽出し、その影響が懸念される箇所をAnsys SIwaveで解析することで、ESD印加時の電圧変動を定量的に評価することが可能となりました。

本事例では、保護キャパシタの追加やグランドシールドパターンの適用により、リセットラインの電圧変動が大幅に低減し、ノイズ影響の改善を確認しました。これにより、ルールチェック結果に基づく対策の有効性を裏付けるとともに、設計判断の精度向上と効率的なESD対策検討に寄与します。