資料ダウンロード

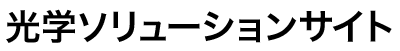

光トランシーバの回路の熱連成シミュレーション

熱の影響を考慮した高信頼性設計支援。光電融合やCPOへの応用も可能

こんな方におすすめ

- 光トランシーバの開発者の方

- 光送信機や光受信機の開発者の方

- 熱を考慮した光回路解析にご興味をお持ちの方

解析概要

本記事では、Ansy app.Galleryにあるサンプル事例(Thermally aware photonic circuit simulation of a WDM transceiver – Icepak integration – Ansys Optics)について詳細を解説します。プリント回路基板(PCB:Printed Circuit Board)に実装された光トランシーバについて、電子集積回路から発生する熱の影響を考慮した回路シミュレーションを行います。まずは、電子集積回路の発熱を考慮したPCB上の温度分布をAnsys Icepakでシミュレーションし、次にその結果をAnsys Lumerical INTERCONNECT に反映させ、回路シミュレーションを行います。

使用ソフトウェア

Ansys Lumerical(INTERCONNECT)

Ansys Icepak

背景/課題

通信の高速化や低消費電力化の阻害要因である電気配線長を短くするために、電気-光の信号変換を担う光トランシーバを電子集積回路の近傍に配置するCPO(Co-Packaged Optics)や、光電融合などの技術開発が盛んに行われています。電子集積回路は高速信号処理などの高度で複雑な機能を担うことから発熱量が大きくなるため、CPOや光電融合では電子集積回路が発生させる熱の影響を考慮した設計が必要となります。

解析対象

電子集積回路の発熱の影響を考慮した光トランシーバの性能(光波形、BER=Bit Error Ratio)

解析手法

(1)PCB基板上の熱シミュレーション(Icepack)

(2)光トランシーバの回路シミュレーション(Lumerical INTERCONNECT)

解析モデル・条件及び結果

(1)PCBの熱シミュレーション(Icepak)

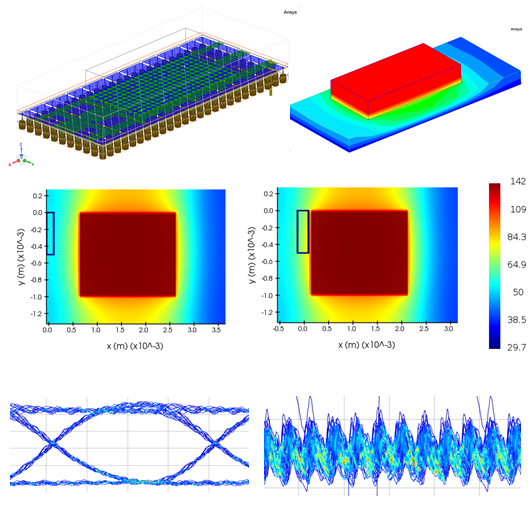

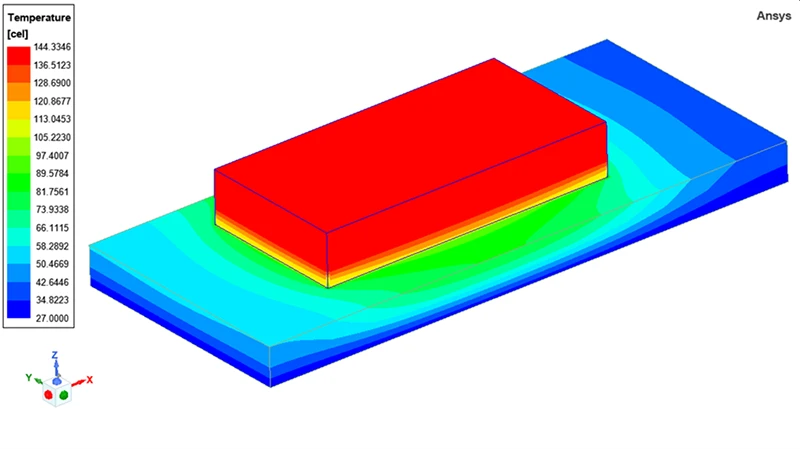

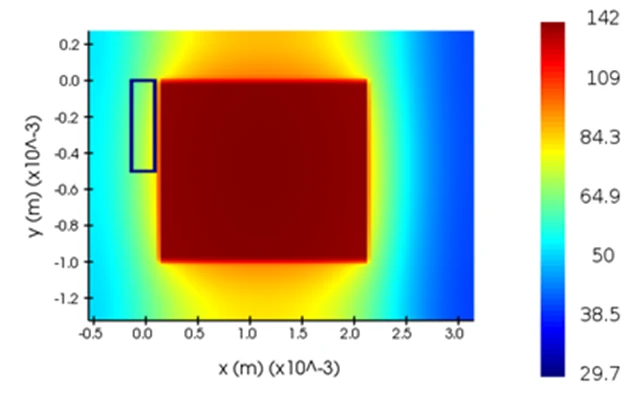

まずは、Icepakを用いた熱シミュレーションを行います。図1にモデルを示します。

図1 PCB及び電子集積回路のモデル

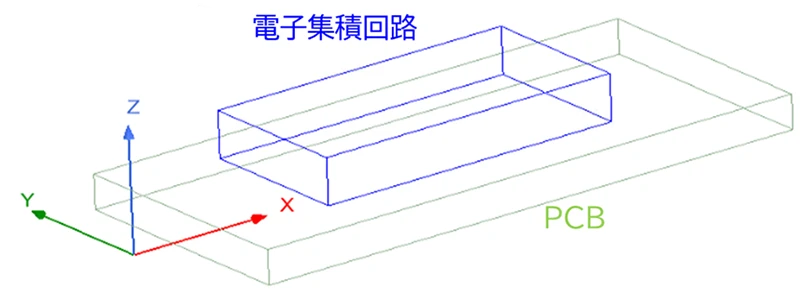

図2に、熱解析の設定画面を示します。左側のProject Managerウィンドウにおける、「Thermal」配下の「ConstantTemp」、「EIC」、「StationaryWall」の3つの設定を行います。図の中央には、モデルにおける該当箇所を、右側には設定画面を示します。「ConstantTemp」では、PCB底面の温度を27℃に固定します。「EIC」では電子集積回路の発熱量を5Wに設定します。「StationaryWall」では、電子集積回路上面の境界条件として、空気による自然対流を設定します。

図2 固有モード解析の設定画面

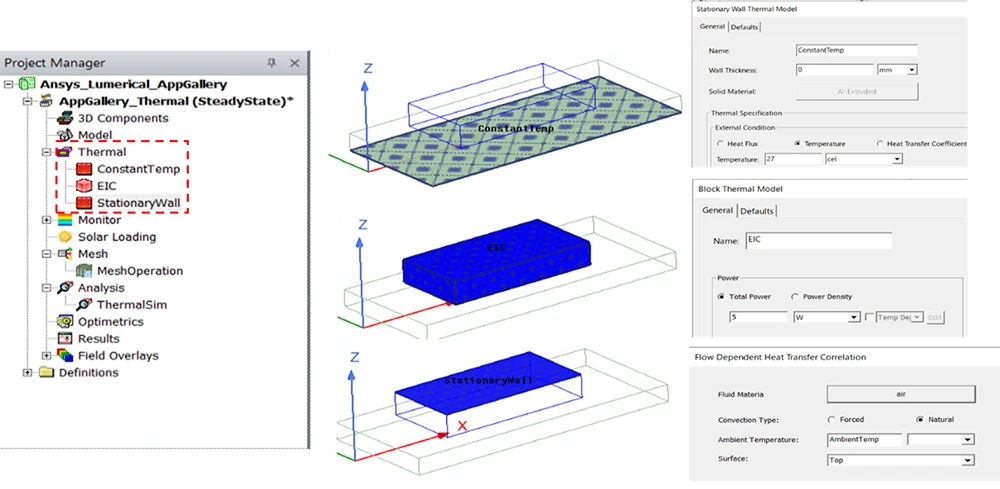

図3が、この条件でシミュレーションを行った結果となります。

図3 温度分布のシミュレーション結果

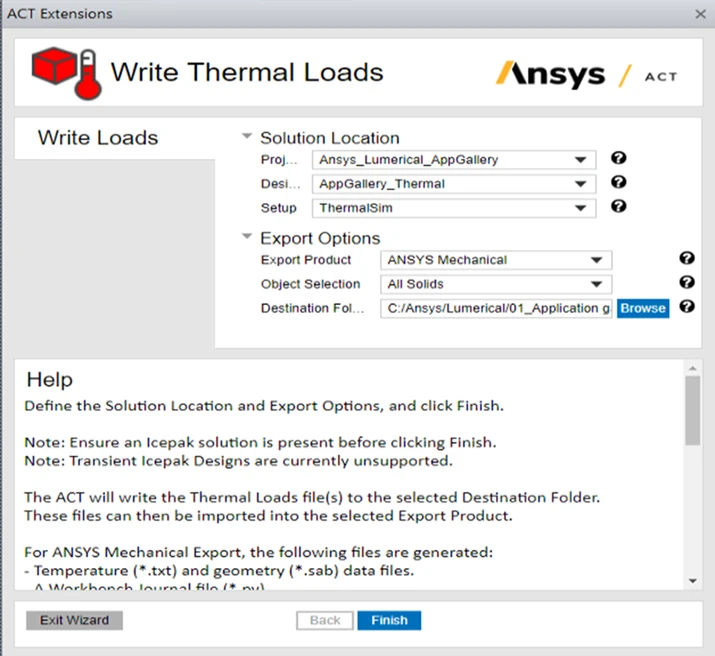

この結果をエクスポートするために、Ansys ACT Extensionsの”Write Thermal Loads”を使用します。Ansys ACT ExtensionsはAnsys上で使用可能なアプリで、”Write Thermal Loads”はAnsys App Storeにおいて無料でダウンロード可能です。

ACT Extensionの詳細や、Ansys App Storeへのアクセス方法などについては、Ansys社が公開している下記リンクの動画をご参照ください。

https://www.youtube.com/watch?v=iqoqqQRMXJk

図4は「Write Thermal Loads」の設定画面です。ファイルの保存場所であるDestination Folderなどの設定を行い、図下部のFinishボタンを押すことで、温度分布ファイルが作成されます。

図4 Write Thermal Loadsの設定画面

(2)光トランシーバの回路シミュレーション(Lumerical INTERCONNECT)

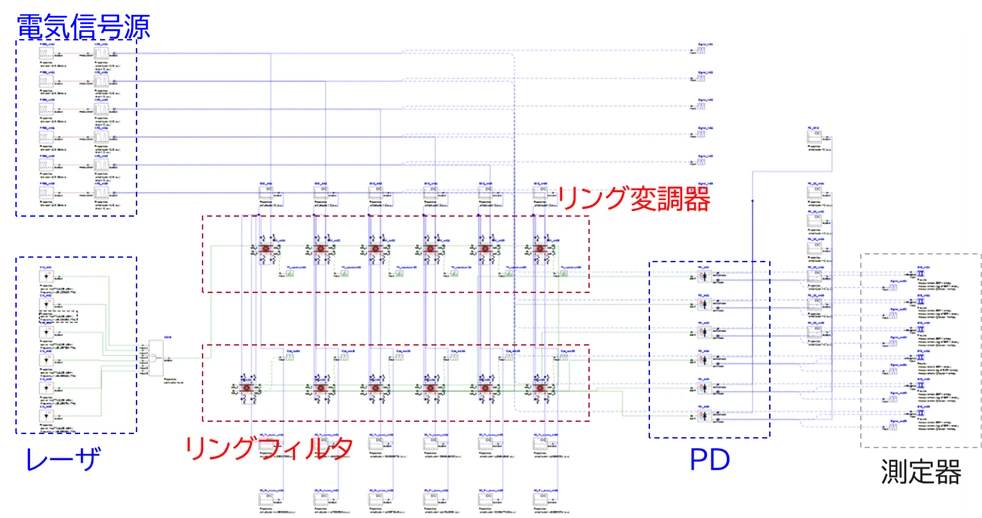

続いて、Lumerical INTERCONNECTによる回路シミュレーションを行います。図5に6波長多重光トランシーバの回路モデルを示します。レーザの光出力(波長の異なる6つの光信号)を一つに束ね、カスケード接続した6個のリング変調器で各波長の光を変調します。変調した光は、リングフィルタで波長毎に取り出され、PDによって電気信号に変換され、最後に測定器で波形解析されます。

図5 6波長多重光トランシーバの回路モデル

回路に使用する光コンポーネント(リング変調器やリングフィルタ、PD)には、概要欄に記載のリンクでダウンロード可能なCML(Compact Model Library)を使用しており、設定温度に応じて自動的に性能が変化します。

CMLはLumerical CML Compilerで作成可能で、Foundryなどから提供されたデータを使用することもできます。

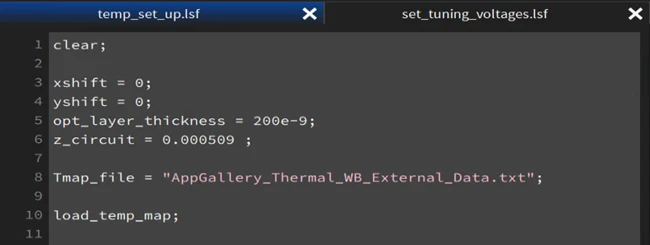

まずは、光トランシーバがデフォルトの位置にある場合の解析を行います。図6に示したLumerical専用言語で書かれたスクリプトでは、先の解析で取得した温度分布(”AppGallery_Thermal_WB_External_Data.txt”)をインポートしPCB上の温度分布をプロットすると共に、各光コンポーネントに温度を設定します。

図6 Lumericalスクリプト

PCB上の温度分布を図7に示します。青い枠は光回路の位置を示しています。

図7 PCB上の温度分布と光回路の位置

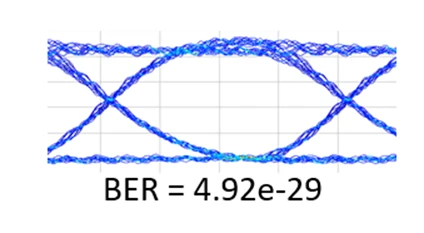

この状態で解析したときの、Ch1の波形及びBER(Bit Error Ratio)は図8の通りです。

図8 Ch1の波形及びBER

続いて、光回路が発熱源であるEICに0.5mm近づいた場合(図6 のスクリプトにおいてx_shift=-0.5e-3に変更した場合)について考えます。温度分布と光回路の位置は図9に示す通りです。

図9 PCB上の温度分布と光回路の位置

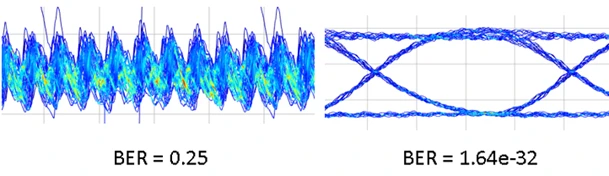

リング変調器やリングフィルタには、電圧チューニングによって温度補償する機能が備わっています。ここでは、電圧値に先の解析(光回路がデフォルト位置:x_shift=0の場合)と同じ値を使う場合と、温度に応じた適切な値に設定する場合の両方について波形解析を行います。電圧チューニングはスクリプトで行いますが、スクリプトファイルは、概要欄記載のリンクにてダウンロード可能ですので、詳細についてはそちらをご確認ください。

図10に、波形及びBERの比較結果を示します。左側が電圧チューニングを行わなかった場合、右側が電圧チューニングを行った場合の結果となります。

図10 波形解析の結果(左:電圧チューニング無し、右:電圧チューニング有り)

まとめ

6波長多重の光トランシーバにおいて、温度の影響を考慮した統合解析を行いました。まずAnsys Icepakで熱解析を行い、発熱源や境界条件に基づいた温度分布を算出し、その結果をAnsys Lumerical INTERCONNECTに取り込み、温度の影響を反映した光回路シミュレーションを実施しました。これにより、温度が光学特性に与える影響を精度高く評価し、信頼性の高い設計が可能となります。

本解析の効果

- 熱による性能劣化の事前予測ができます。

- 温度分布に基づいた最適設計を行うことができます。

- 製品信頼性の向上が期待されます。

- マルチフィジクス連携による高精度な設計を行うことができます。

※内容の詳細は、下記ボタンより資料ダウンロード頂けます。