Bluespecとは?

Bluespecは、アーキテクチャ設計、インプリメント、ベリフィケーションにおいて、HW設計者の要求に応える設計環境を提供し、LSI開発に劇的な効果をもたらします。

近年、製品の高機能化はとどまることなく、システムの複雑さが増大の一途をたどっています。この高機能化により、ASIC/FPGAの開発には新たな手法が求められています。新たな手法として、RTL 記述の抽象度を上げシステムレベルでの設計が行われていますが、なかなか浸透していないのが現状です。

これは、H/W 設計者には馴染み難いC 言語ベースという理由もありますが、制御系の回路では設計者の意図を詳細に反映したH/W化が非常に煩雑であることが大きな理由です。RTLとシステムレベル、この間の抽象度ギャップは非常に大きく、従来の手法ではその差を埋めることはとても大変です。システムレベルからRTLへのH/Wトランスペアレンシーを保証する、RTL 設計者のための新たな手法が鍵となるのではないでしょうか。

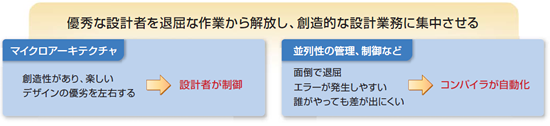

Bluespecのポリシー

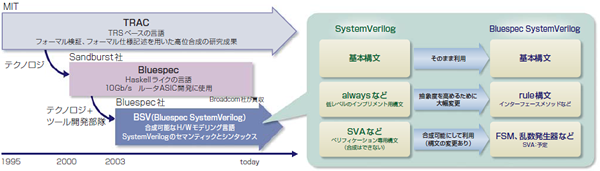

そこで開発されたのがBluespec System Verilog(BSV)です。

BSVはMIT(Massachusetts Institute of Technology)で開発された革新的な言語であり、RTLよりも抽象度が高く、完全な並列性が表現できます。また、高速なシミュレーションとリファイメント性も兼ね備えています。BSV で記述されたモデルは、全て合成可能であり、システムレベル記述からのH/W実装を実現することが可能です。つまり、BSV はRTL とシステムレベルップをH/Wの設計思想をベースにした実行可能なモデルでうめることにより、大規模・複雑化するLSI 開発の救世主となります。

製品構成

Bluespecは高位合成ツール「Bluespec Compiler」とシミュレータ「Bluesim」が含まれます。

- 入力言語は、BSV(Bluespec System Verilog)

- 論理合成可能なverilog RTLへ合成

- BSVで書かれたテストベンチは、RTLへ合成可能

- 設計制約ファイルは不要

- RTLレベルのSystemCを合成可能

- BSVで記述されたモデルを検証するためのシミュレータ

- サイクルベース

- RTLシミュレータの3〜10倍高速

| 製品情報 | |

| カタログ・トライアル版 | |

| お問い合わせ |