解析事例

同時スイッチングノイズ解析

こんな方におすすめ

- 高速伝送線路におけるパワーインテグリティの影響を考慮したインターコネクト・PCB設計者

PCBの信号配線、電源グランドプレーンを考慮して、ドライバを同時スイッチングしたときのドライバ内部電源端子に発生する電源ノイズ解析結果を紹介します。

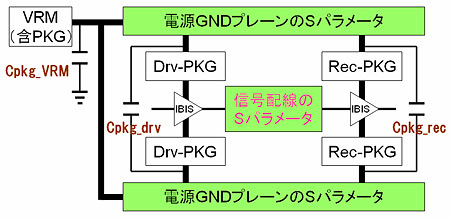

- 図1は同時スイッチングノイズシミュレーション回路の全体ブロック図を示したものです。

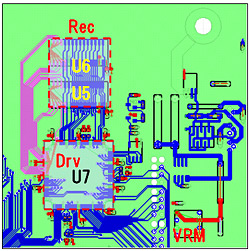

このブロック図の緑色の部分はSIwaveにより、信号配線および電源グランドプレーンのPCBレイアウトデータから抽出したSパラメータを用いています。 - 図2はSiwaveに於ける信号線、電源グランドプレーンを含むPCBレイアウトインポートデータです。

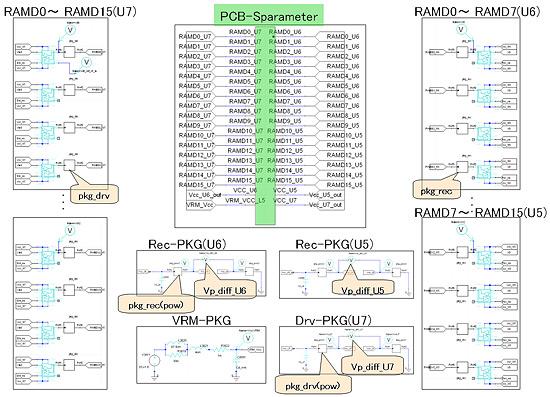

- 図3はDesigner の同時スイッチングノイズのシミュレーション回路図です。

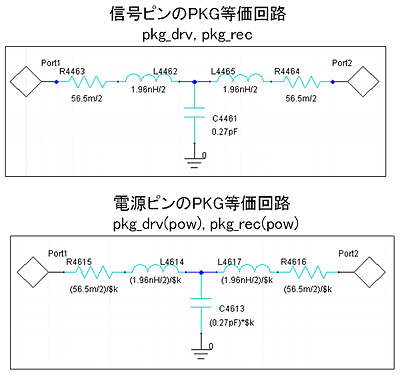

- 図4は信号ピン、電源グランドピンのPKG等価回路図です。i/Oバッファの電源グランド端子に電源ピンのPKG等価回路を挿入しており、ドライバの同時駆動信号の本数を4,8,16としてシミュレーションを行います。

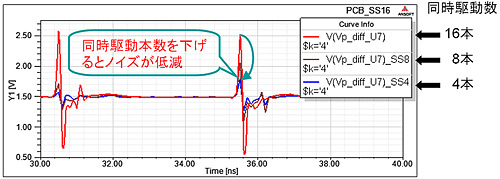

- 図5は同時スイッチングノイズ解析結果です。同時駆動本数が多くなるに従い、電源端子のノイズ振幅は大きくなっているのが確認できます。また、スイッチングノイズを小さくするにはPKGインピーダンスをできる限り小さくすることが望ましいと云えます。